www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

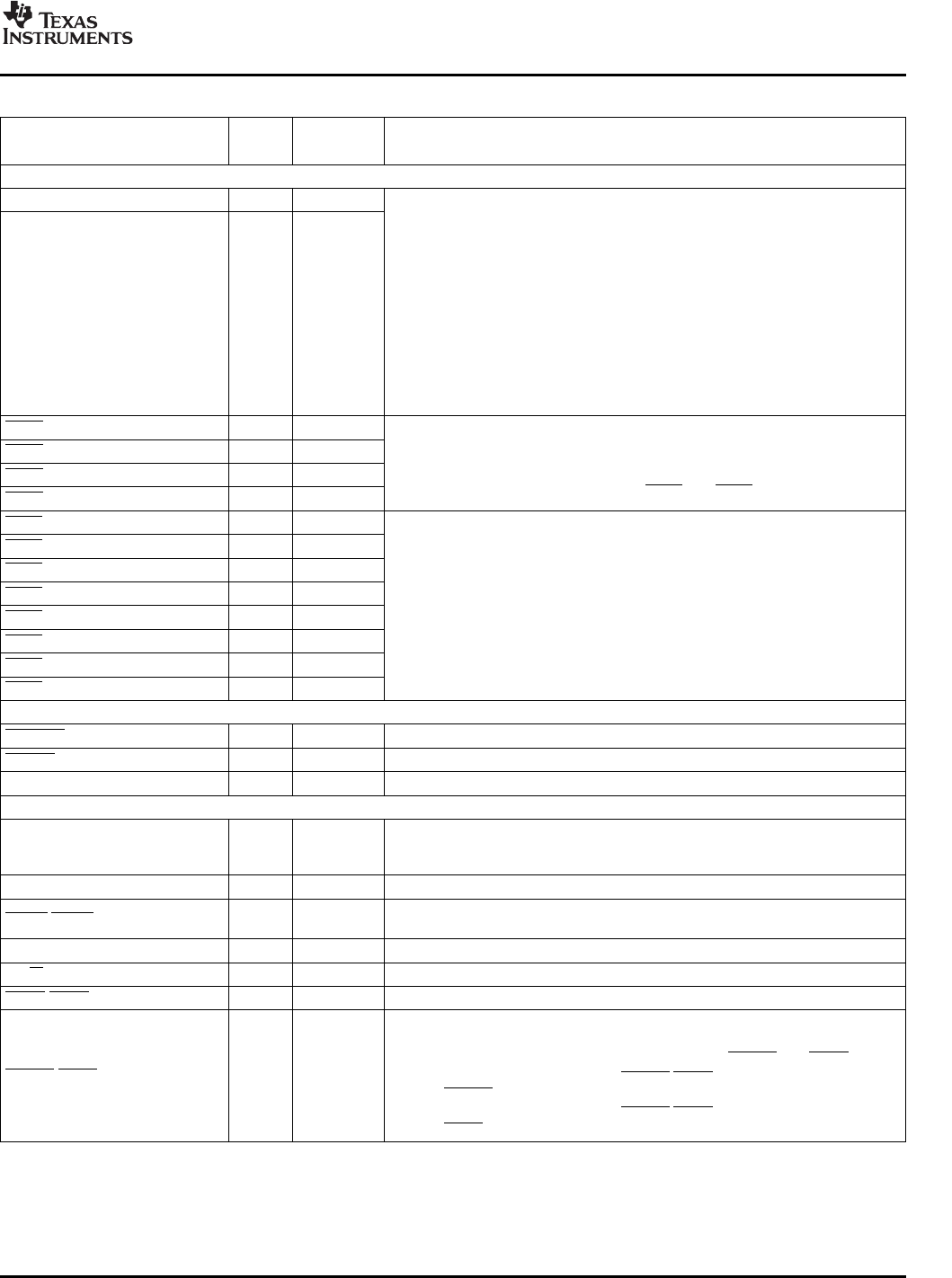

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

EMIFA(64BIT)-CONTROLSIGNALSCOMMONTOALLTYPESOFMEMORY

ABA1/EMIFA_ENV25O/ZIPDEMIFAbankaddresscontrol(ABA[1:0])

•Active-lowbankselectsforthe64bitEMIFA.

Wheninterfacingto16bitAsynchronousdevices,ABA1carriesbit1ofthe

byteaddress.

Foran8bitAsynchronousinterface,ABA[1:0]areusedtocarrybits1and

0ofthebyteaddress

DDR2MemoryControllerenable(DDR2_EN)[ABA0]

ABA0/DDR2_ENV26O/ZIPD

0-DDR2MemoryControllerperipheralpinsaredisabled(default)

1-DDR2MemoryControllerperipheralpinsareenabled

EMIFAenable(EMIFA_EN)[ABA1]

0-EMIFAperipheralpinsaredisabled(default)

1-EMIFAperipheralpinsareenabled

ACE5V27O/ZIPU

EMIFAmemoryspaceenables

ACE4V28O/ZIPU

•Enabledbybits28through31ofthewordaddress

ACE3W26O/ZIPU

•Onlyonepinisassertedduringanyexternaldataaccess

Note:TheC6455devicedoesnothaveACE0andACE1pins

ACE2W27O/ZIPU

ABE7W29O/ZIPU

ABE6K26O/ZIPU

ABE5L29O/ZIPU

EMIFAbyte-enablecontrol

ABE4L28O/ZIPU

•Decodedfromthelow-orderaddressbits.Thenumberofaddressbitsor

byteenablesuseddependsonthewidthofexternalmemory.

ABE3AA29O/ZIPU

•Byte-writeenablesformosttypesofmemory.

ABE2AA28O/ZIPU

ABE1AA25O/ZIPU

ABE0AA26O/ZIPU

EMIFA(64BIT)-BUSARBITRATION

AHOLDAN26OIPUEMIFAhold-request-acknowledgetothehost

AHOLDR29IIPUEMIFAholdrequestfromthehost

ABUSREQL27OIPUEMIFAbusrequestoutput

EMIFA(64BIT)-ASYNCHRONOUS/SYNCHRONOUSMEMORYCONTROL

EMIFAexternalinputclock.TheEMIFAinputclock(AECLKINorSYSCLK4

AECLKINN29IIPDclock)isselectedatresetviathepullup/pulldownresistorontheAEA[15]pin.

Note:AECLKINisthedefaultfortheEMIFAinputclock.

AECLKOUTV29O/ZIPDEMIFAoutputclock[atEMIFAinputclock(AECLKINorSYSCLK4)frequency]

Asynchronousmemorywrite-enable/Programmablesynchronousinterface

AAWE/ASWEAB25O/ZIPU

write-enable

AARDYK29IIPUAsynchronousmemoryreadyinput

AR/WW25O/ZIPUAsynchronousmemoryread/write

AAOE/ASOEY28O/ZIPUAsynchronous/Programmablesynchronousmemoryoutput-enable

Programmablesynchronousaddressstrobeorread-enable

•Forprogrammablesynchronousinterface,theR_ENABLEfieldintheChip

SelectxConfigurationRegisterselectsbetweenASADSandASRE:

ASADS/ASRER26O/ZIPU

–IfR_ENABLE=0,thentheASADS/ASREsignalfunctionsasthe

ASADSsignal.

–IfR_ENABLE=1,thentheASADS/ASREsignalfunctionsasthe

ASREsignal.

SubmitDocumentationFeedbackDeviceOverview33