www.ti.com

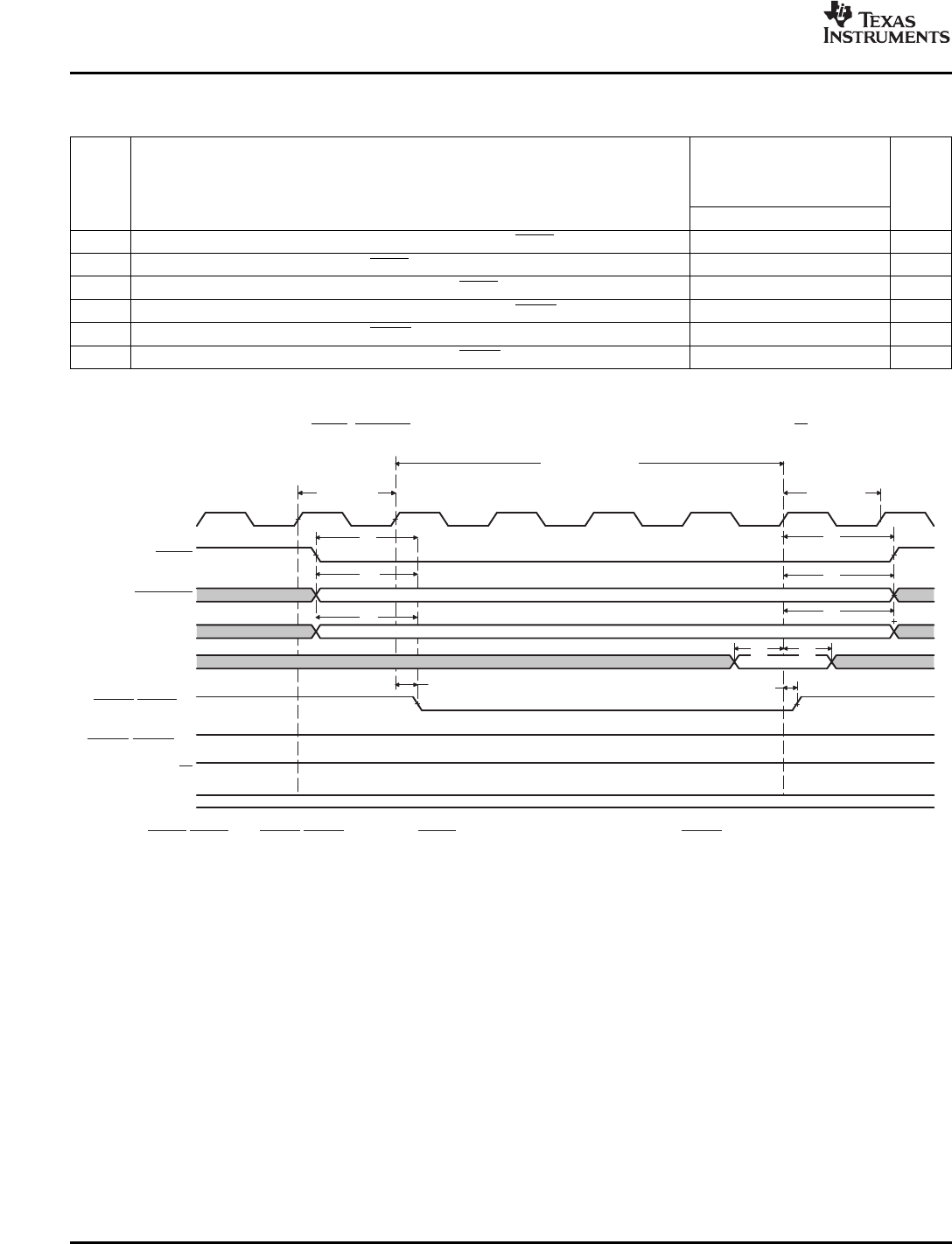

AECLKOUT

ACEx

ABE[7:0]

AEA[19:0]/

ABA[1:0]

AED[63:0]

AAOE/ASOE

(A)

AR/W

AAWE/ASWE

(A)

AARDY

(B)

Byte Enables

Address

Read Data

Hold = 1

2

Strobe = 4

Setup = 1

2

2

4

10

10

1

1

1

3

A AAOE/ASOE and AAWE/ASWE operate as AAOE (identified under select signals) and AAWE, respectively, during asynchronous

memory accesses.

B Polarity of the AARDY signal is programmable through the AP field of the EMIFA Async Wait Cycle Configuration register (AWCC).

DEASSERTED

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

Table7-45.SwitchingCharacteristicsOverRecommendedOperatingConditionsforAsynchronous

MemoryCyclesforEMIFAModule

(1)(2)(3)

(seeFigure7-33andFigure7-34)

-720

-850

A-1000/-1000

NO.PARAMETERUNIT

-1200

MINMAX

1t

osu(SELV-AOEL)

Outputsetuptime,selectsignalsvalidtoAAOElowRS*E–1.5ns

2t

oh(AOEH-SELIV)

Outputholdtime,AAOEhightoselectsignalsinvalidRS*E–1.9ns

10t

d(EKOH-AOEV)

Delaytime,AECLKOUThightoAAOEvalid17ns

11t

osu(SELV-AWEL)

Outputsetuptime,selectsignalsvalidtoAAWElowWS*E–1.7ns

12t

oh(AWEH-SELIV)

Outputholdtime,AAWEhightoselectsignalsinvalidWH*E–1.8ns

13t

d(EKOH-AWEV)

Delaytime,AECLKOUThightoAAWEvalid1.37.1ns

(1)E=AECLKOUTperiodinnsforEMIFA

(2)RS=Readsetup,RST=Readstrobe,RH=Readhold,WS=Writesetup,WST=Writestrobe,WH=Writehold.Theseparameters

areprogrammedviatheEMIFACEConfigurationregisters(CEnCFG).

(3)SelectsignalsforEMIFAinclude:ACEx,ABE[7:0],AEA[19:0],ABA[1:0];andforEMIFAwrites,alsoincludeAR/W,AED[63:0].

Figure7-33.AsynchronousMemoryReadTimingforEMIFA

C64x+PeripheralInformationandElectricalSpecifications 166SubmitDocumentationFeedback