www.ti.com

7.5Interrupts

7.5.1InterruptSourcesandInterruptController

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

TheCPUinterruptsontheC6455deviceareconfiguredthroughtheC64x+MegamoduleInterrupt

Controller.Theinterruptcontrollerallowsforupto128systemeventstobeprogrammedtoanyofthe

twelveCPUinterruptinputs(CPUINT4-CPUINT15),theCPUexceptioninput(EXCEP),ortheadvanced

emulationlogic.The128systemeventsconsistofbothinternally-generatedevents(withinthe

megamodule)andchip-levelevents.Table7-10showsthemappingofsystemevents.Formore

informationontheInterruptController,seetheTMS320C64x+MegamoduleReferenceGuide(literature

numberSPRU871).

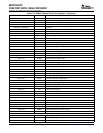

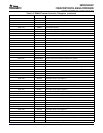

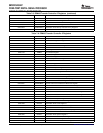

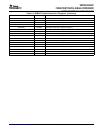

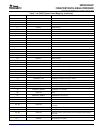

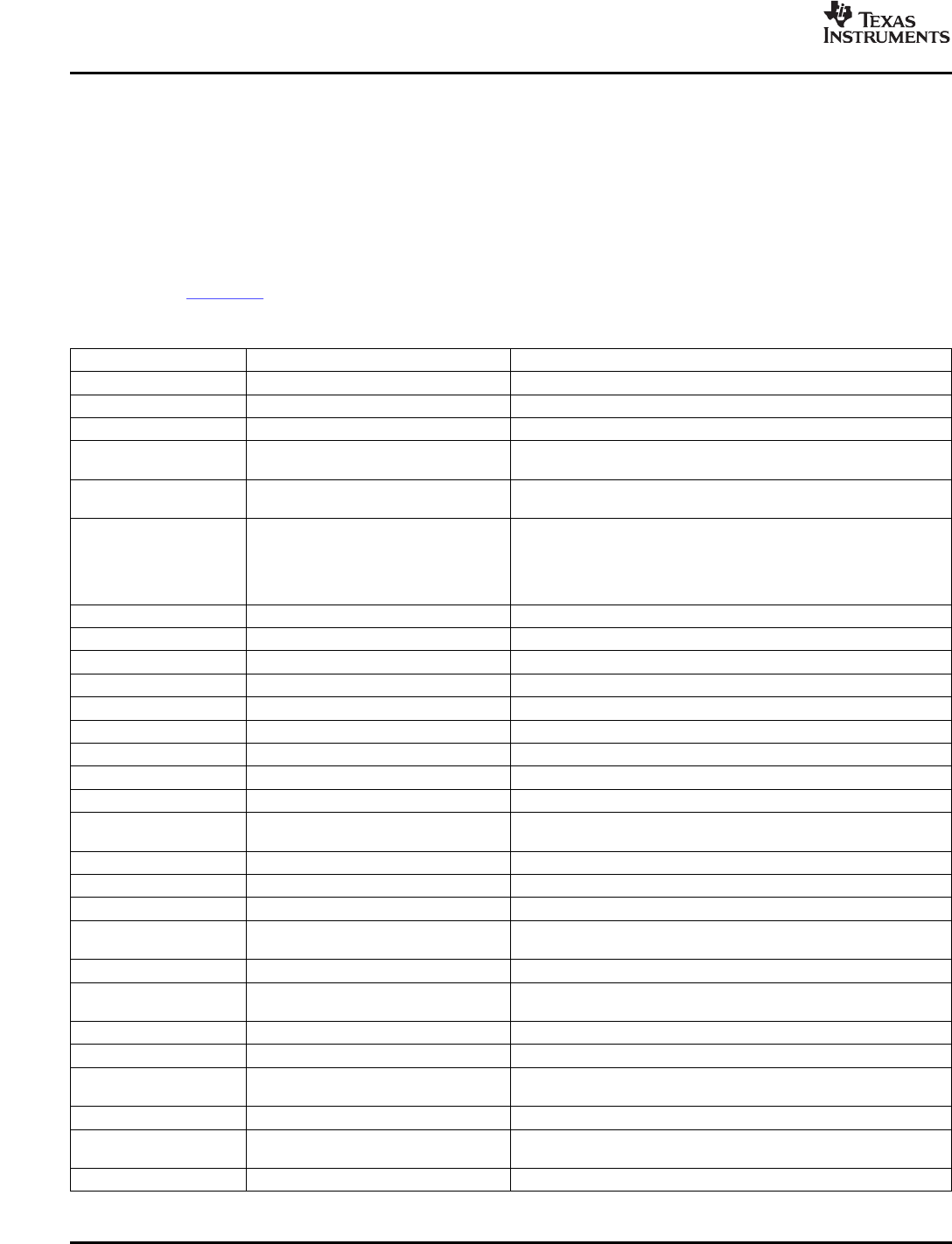

Table7-10.C6455SystemEventMapping

EVENTNUMBERINTERRUPTEVENTDESCRIPTION

0

(1)

EVT0Outputofeventcombiner0ininterruptcontroller,forevents1-31.

1

(1)

EVT1Outputofeventcombiner1ininterruptcontroller,forevents32-63.

2

(1)

EVT2Outputofeventcombiner2ininterruptcontroller,forevents64-95.

Outputofeventcombiner3ininterruptcontroller,forevents96-

3

(1)

EVT3

127.

Reserved.Thesesystemeventsarenotconnectedand,therefore,

4-8Reserved

notused.

EMUinterruptfor:

1.Hostscanaccess

9

(1)

EMU_DTDMA

2.DTDMAtransfercomplete

3.AETinterrupt

10NoneThissystemeventisnotconnectedand,therefore,notused.

11

(1)

EMU_RTDXRXEMUreal-timedataexchange(RTDX)receivecomplete

12

(1)

EMU_RTDXTXEMURTDXtransmitcomplete

13

(1)

IDMA0IDMAchannel0interrupt

14

(1)

IDMA1IDMAchannel1interrupt

15DSPINTHPI/PCI-to-DSPinterrupt

16I2CINTI2Cinterrupt

17MACINTEthernetMACinterrupt

18AEASYNCERREMIFAerrorinterrupt

Reserved.Thissystemeventisnotconnectedand,therefore,not

19Reserved

used.

20INTDST0RapidIOinterrupt0

21INTDST1RapidIOinterrupt1

22INTDST4RapidIOinterrupt4

Reserved.Thissystemeventisnotconnectedand,therefore,not

23Reserved

used.

24EDMA3CC_GINTEDMA3channelglobalcompletioninterrupt

Reserved.Thesesystemeventsarenotconnectedand,therefore,

25-31Reserved

notused.

32VCP2_INTVCP2errorinterrupt

33TCP2_INTTCP2errorinterrupt

Reserved.Thesesystemeventsarenotconnectedand,therefore,

34-35Reserved

notused.

36UINTUTOPIAinterrupt

Reserved.Thesesystemeventsarenotconnectedand,therefore,

37-39Reserved

notused.

40RINT0McBSP0receiveinterrupt

(1)ThissystemeventisgeneratedfromwithintheC64x+megamodule.

C64x+PeripheralInformationandElectricalSpecifications 124SubmitDocumentationFeedback