www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

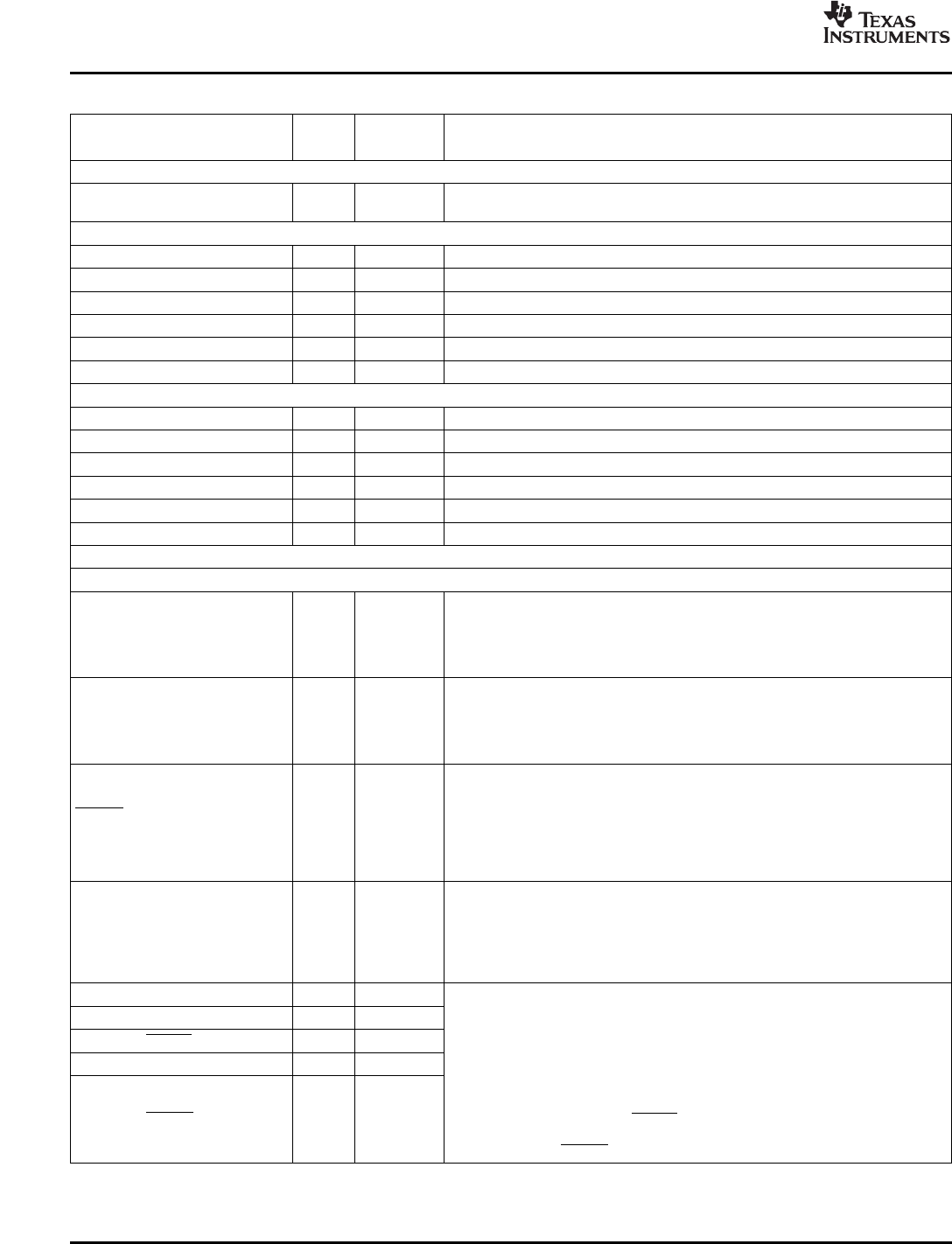

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

MULTICHANNELBUFFEREDSERIALPORT1ANDMULTICHANNELBUFFEREDSERIALPORT0(McBSP1andMcBSP0)

McBSPexternalclocksource(asopposedtointernal)(I)

CLKSAJ4IIPD

[sharedbyMcBSP1andMcBSP0]

MULTICHANNELBUFFEREDSERIALPORT1(McBSP1)

CLKR1/GP[0]AF4I/O/ZIPDMcBSP1receiveclock(I/O/Z)orGP[0](I/O/Z)[default]

FSR1/GP[10]AE5I/O/ZIPDMcBSP1receiveframesync(I/O/Z)orGP[10](I/O/Z)[default]

DR1/GP[8]AH5I/O/ZIPDMcBSP1receivedata(I)orGP[8](I/O/Z)[default]

DX1/GP[9]AG5I/O/ZIPDMcBSP1transmitdata(O/Z)orGP[9](I/O/Z)[default]

FSX1/GP[11]AG4I/O/ZIPDMcBSP1transmitframesync(I/O/Z)orGP[11](I/O/Z)[default]

CLKX1/GP[3]AF5I/O/ZIPDMcBSP1transmitclock(I/O/Z)orGP[3](I/O/Z)[default]

MULTICHANNELBUFFEREDSERIALPORT0(McBSP0)

CLKR0AG1I/O/ZIPUMcBSP0receiveclock(I/O/Z)

FSR0AH3I/O/ZIPDMcBSP0receiveframesync(I/O/Z)

DR0AJ5IIPDMcBSP0receivedata(I)

DX0AF6I/O/ZIPDMcBSP0transmitdata(O/Z)

FSX0AJ3I/O/ZIPDMcBSP0transmitframesync(I/O/Z)

CLKX0AG6I/O/ZIPUMcBSP0transmitclock(I/O/Z)

UNIVERSALTESTANDOPERATIONSPHYINTERFACEforASYNCHRONOUSTRANSFERMODE(ATM)[UTOPIASLAVE]

UTOPIASLAVE(ATMCONTROLLER)-TRANSMITINTERFACE

SourceclockforUTOPIAtransmitdrivenbyMasterATMController.

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

UXCLK/MTCLK/

N4I/O/ZpiniseitherEMACMIItransmitclock(MTCLK)ortheEMACRMIIreference

RMREFCLK

clock.TheEMACfunctioniscontrolledbytheMACSEL[1:0](AEA[10:9]pins).

Formoredetailedinformation,seeSection3,DeviceConfiguration.

TransmitcellavailablestatusoutputsignalfromUTOPIASlave.

0indicatesacompletecellisNOTavailablefortransmit

UXCLAV/GMTCLKK5I/O/Z1indicatesacompletecellisavailablefortransmit

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACGMIItransmitclock.MACSEL[1:0]dependent.

UTOPIAtransmitinterfaceenableinputsignal.AssertedbytheMasterATM

ControllertoindicatethattheUTOPIASlaveshouldputoutontheTransmit

DataBusthefirstbyteofvaliddataandtheUXSOCsignalinthenextclock

UXENB/MTXEN/

J5I/O/Zcycle.

RMTXEN

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

piniseithertheEMACMIItransmitenable[default]orEMACRMIItransmit

enableorEMACGMIItransmitenable.MACSEL[1:0]dependent.

TransmitStart-of-Cellsignal.ThissignalisoutputbytheUTOPIASlaveonthe

risingedgeoftheUXCLK,indicatingthatthefirstvalidbyteofthecellis

availableonthe8bitTransmitDataBus(UXDATA[7:0]).

UXSOC/MCOLK3I/O/Z

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

piniseithertheEMACMIIcollisionsenseorEMACGMIIcollisionsense.

MACSEL[1:0]dependent.

UXADDR4/MDCLKM5IUTOPIAtransmitaddresspins(UXADDR[4:0])(I)

AsUTOPIAtransmitaddresspins,UTOPIA_EN(AEA12pin)=1:

UXADDR3/MDION3I

•5bitSlavetransmitaddressinputpinsdrivenbytheMasterATMController

UXADDR2/PCBE3P5I

toidentifyandselectoneoftheSlavedevices(upto31possible)inthe

ATMSystem.

UXADDR1/PIDSELR3I

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0)andif

thePCI_ENpin=1,thesepinsarePCIperipheralpins:

UXADDR0/PTRDYP4I

PCIcommand/byteenable3(PCBE3)[I/O/Z],

PCIinitializationdeviceselect(PIDSEL)[I],and

PCItargetready(PTRDY)[I/O/Z].

DeviceOverview 40SubmitDocumentationFeedback