www.ti.com

3.4.2PeripheralConfigurationRegister0Description

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

ThePeripheralConfigurationRegister(PERCFG0)isusedtochangethestateoftheperipherals.One

writeisallowedtothisregisterwithin16SYSCLK3cyclesafterthecorrectkeyiswrittentothePERLOCK

register.

NOTE

TheinstructionsthatwritetothePERLOCKandPERCFG0registersmustbeinthesame

fetchpacketifcodeisbeingexecutedfromexternalmemory.Iftheinstructionsarein

differentfetchpackets,fetchingthesecondinstructionfromexternalmemorymaystallthe

instructionlongenoughsuchthatPERCFG0registerwillbelockedbeforetheinstruction

isexecuted.

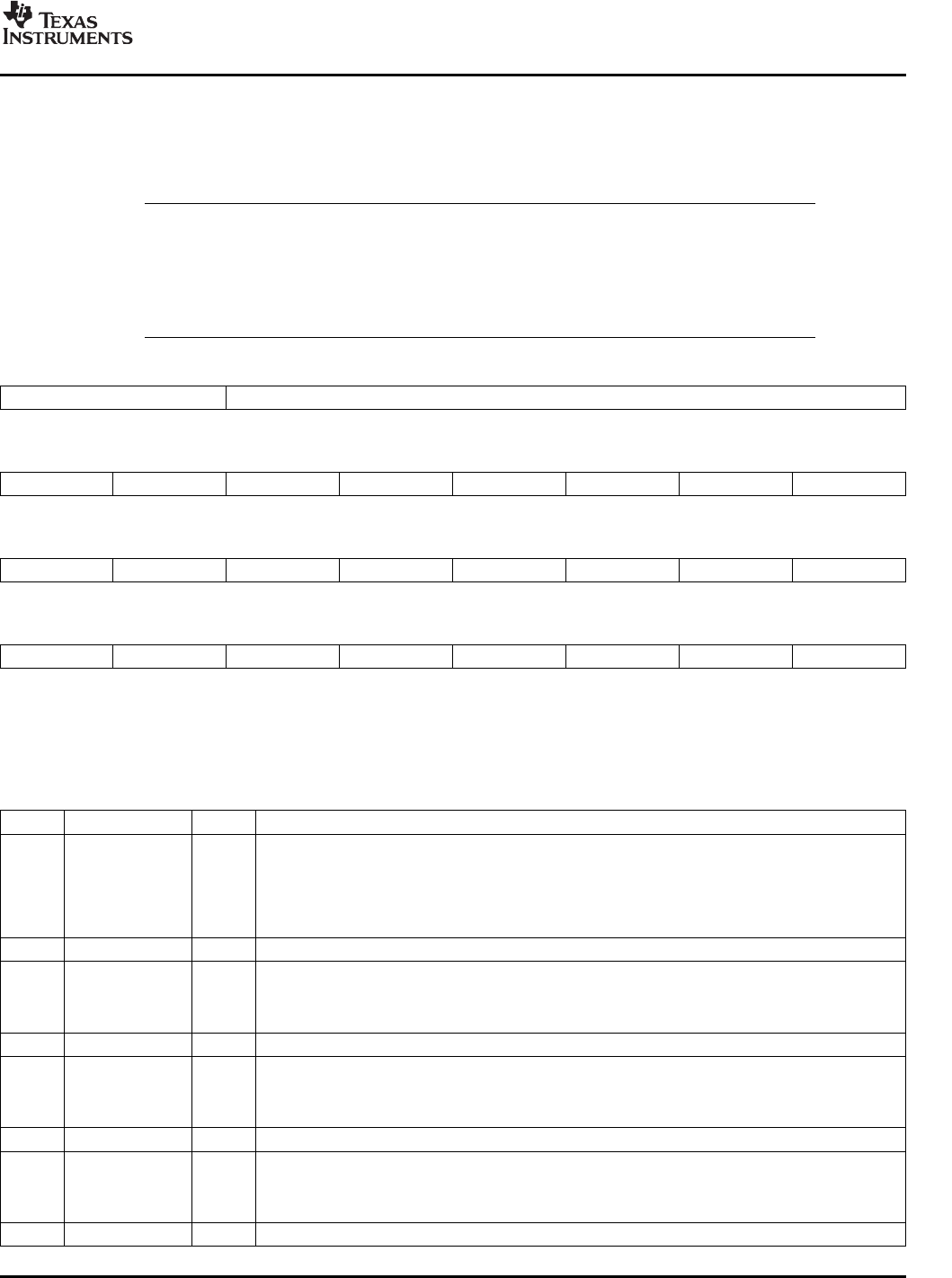

31302924

SRIOCTLReserved

R/W-0R/W-0

2322212019181716

ReservedUTOPIACTLReservedPCICTLReservedHPICTLReservedMcBSP1CTL

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

15141312111098

ReservedMcBSP0CTLReservedI2CCTLReservedGPIOCTLReservedTIMER1CTL

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

76543210

ReservedTIMER0CTLReservedEMACCTLReservedVCPCTLReservedTCPCTL

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Writeonly;-n=valueafterreset

Figure3-4.PeripheralConfigurationRegister0(PERCFG0)-0x02AC0008

Table3-7.PeripheralConfigurationRegister0(PERCFG0)FieldDescriptions

BitFieldValueDescription

31-30SRIOCTLModecontrolforSRIO.SRIOdoesnothaveacorrespondingstatusbitinthePeripheralStatus

Registers.OnceSRIOCTLissetto11b,theSRIOperipheralcanbeusedwithin16SYSCLK3

cycles.

00bSetSRIOtodisabledmode

11bSetSRIOtoenabledmode

29:23ReservedReserved.

22UTOPIACTLModecontrolforUTOPIA

0SetUTOPIAtodisabledmode

1SetUTOPIAtoenabledmode

21ReservedReserved.

20PCICTLModecontrolforPCI.Thisbitdefaultsto1whenHostbootisused(BOOTMODE[3:0]=0111b).

0SetPCItodisabledmode

1SetPCItoenabledmode

19ReservedReserved.

18HPICTLModecontrolforHPI.Thisbitdefaultsto1whenHostbootisused(BOOTMODE[3:0]=0001b).

0SetHPItodisabledmode

1SetHPItoenabledmode

17Reserved1Reserved.

SubmitDocumentationFeedbackDeviceConfiguration67