www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

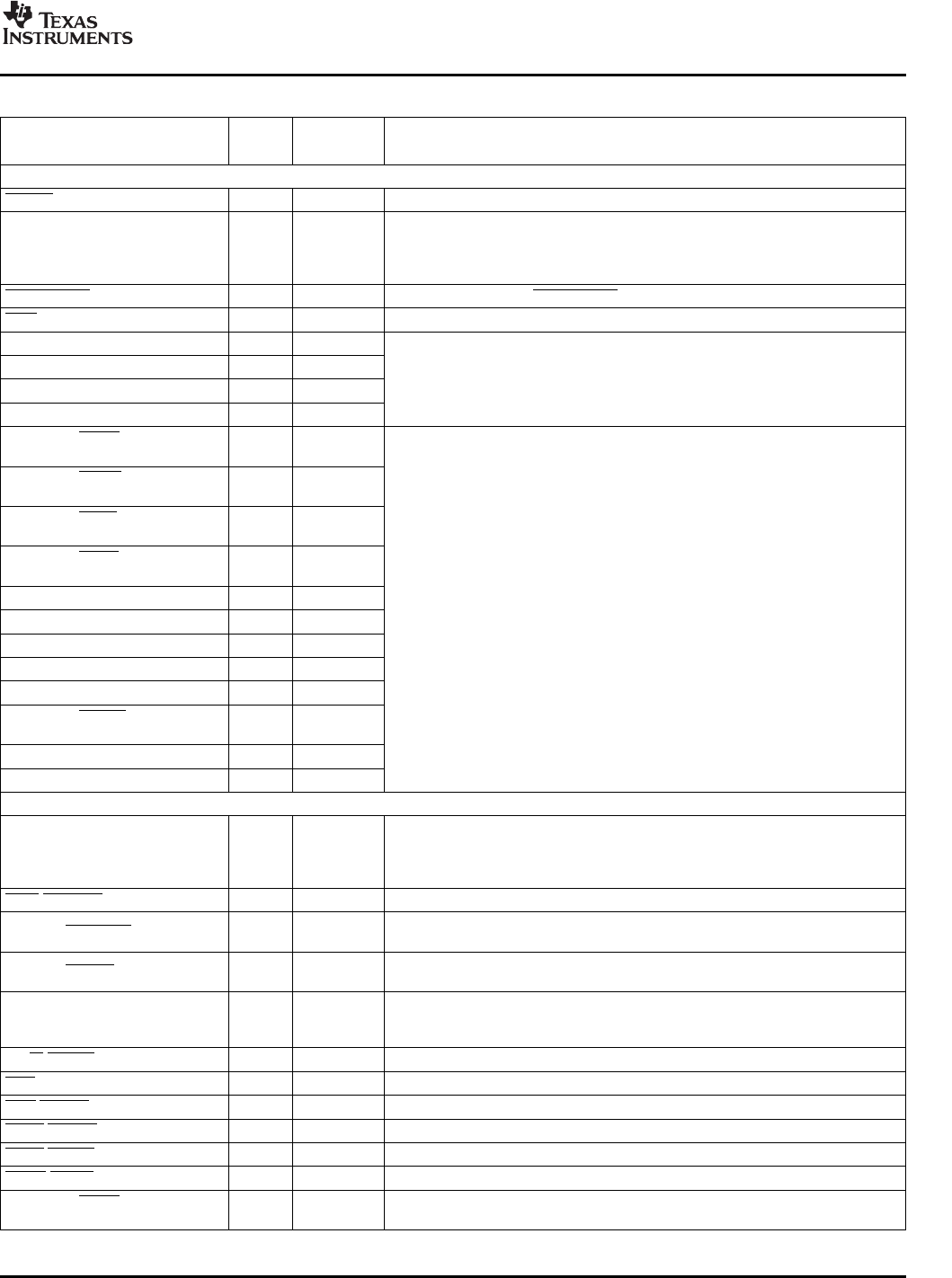

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

RESETS,INTERRUPTS,ANDGENERAL-PURPOSEINPUT/OUTPUTS

RESETAG14IDevicereset

Nonmaskableinterrupt,edge-driven(risingedge)

AnynoiseontheNMIpinmaytriggeranNMIinterrupt;therefore,iftheNMIpin

NMIAH4IIPD

isnotused,itisrecommendedthattheNMIpinbegroundedversusrelyingon

theIPD.

RESETSTATAE14OResetStatuspin.TheRESETSTATpinindicateswhenthedeviceisinreset

PORAF14IPoweronreset.

GP[7]AG2I/O/ZIPD

GP[6]AG3I/O/ZIPD

General-purposeinput/output(GPIO)pins(I/O/Z).

GP[5]AJ2I/O/ZIPD

GP[4]AH2I/O/ZIPD

URADDR3/PREQ/

P2I/O/Z

GP[15]

URADDR2/PINTA

(5)

/

P3I/O/Z

GP[14]

UTOPIAreceivedaddresspinsorPCIperipheralpinsorGeneral-purpose

URADDR1/PRST/

R5I/O/Z

input/output(GPIO)[15:12,2]pins(I/O/Z)[default]

GP[13]

PCIbusrequest(O/Z)orGP[15](I/O/Z)[default]

URADDR0/PGNT/

R4I/O/Z

PCIinterruptA(O/Z)orGP[14](I/O/Z)[default]

GP[12]

PCIreset(I)orGP[13](I/O/Z)[default]

FSX1/GP[11]AG4I/O/ZIPD

PCIbusgrant(I)orGP[12](I/O/Z)[default]

PCIcommand/byteenable0(I/O/Z)orGP[2](I/O/Z)[default]

FSR1/GP[10]AE5I/O/ZIPD

DX1/GP[9]AG5I/O/ZIPD

McBSP1transmitclock(I/O/Z)orGP[3](I/O/Z)[default]

McBSP1receiveclock(I/O/Z)orGP[0](I/O/Z)[default]

DR1/GP[8]AH5I/O/ZIPD

GP[1]pin(I/O/Z).SYSCLK4istheclockoutputat1/8ofthedevicespeed(O/Z)

CLKX1/GP[3]AF5I/O/ZIPD

orthispincanbeprogrammedasaGP[1]pin(I/O/Z)[default].

URADDR4/PCBE0/

P1I/O/Z

GP[2]

SYSCLK4/GP[1]AJ13O/ZIPD

CLKR1/GP[0]AF4I/O/ZIPD

HOST-PORTINTERFACE(HPI)orPERIPHERALCOMPONENTINTERCONNECT(PCI)

PCIenablepin.Thispincontrolstheselection(enable/disable)oftheHPIand

GP[15:8],orPCIperipherals.Thispinworksinconjunctionwiththe

PCI_ENY29IIPD

MCBSP1_EN(AEA5pin)toenable/disableotherperipherals(formoredetails,

seeSection3,DeviceConfiguration).

HINT/PFRAMEU3I/O/ZHostinterruptfromDSPtohost(O/Z)orPCIframe(I/O/Z)

Hostcontrol-selectsbetweencontrol,address,ordataregisters(I)[default]or

HCNTL1/PDEVSELU4I/O/Z

PCIdeviceselect(I/O/Z)

Hostcontrol-selectsbetweencontrol,address,ordataregisters(I)[default]or

HCNTL0/PSTOPU5I/O/Z

PCIstop(I/O/Z)

Hosthalf-wordselect-firstorsecondhalf-word(notnecessarilyhighorlow

HHWIL/PCLKV3I/O/Zorder)

[ForHPI16buswidthselectiononly](I)[default]orPCIclock(I)

HR/W/PCBE2T5I/O/ZHostreadorwriteselect(I)[default]orPCIcommand/byteenable2(I/O/Z)

HAS/PPART3I/O/ZHostaddressstrobe(I)[default]orPCIparity(I/O/Z)

HCS/PPERRU6I/O/ZHostchipselect(I)[default]orPCIparityerror(I/O/Z)

HDS1/PSERR

(5)

U2I/O/ZHostdatastrobe1(I)[default]orPCIsystemerror(I/O/Z)

HDS2/PCBE1U1I/O/ZHostdatastrobe2(I)[default]orPCIcommand/byteenable1(I/O/Z)

HRDY/PIRDYT4I/O/ZHostreadyfromDSPtohost(O/Z)[default]orPCIinitiatorready(I/O/Z)

URADDR3/PREQ/UTOPIAreceivedaddresspin3(URADDR3)(I)orPCIbusrequest(O/Z)or

P2I/O/Z

GP[15]GP[15](I/O/Z)[default]

(5)Thesepinsfunctionasopen-drainoutputswhenconfiguredasPCIpins.

SubmitDocumentationFeedbackDeviceOverview31