www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

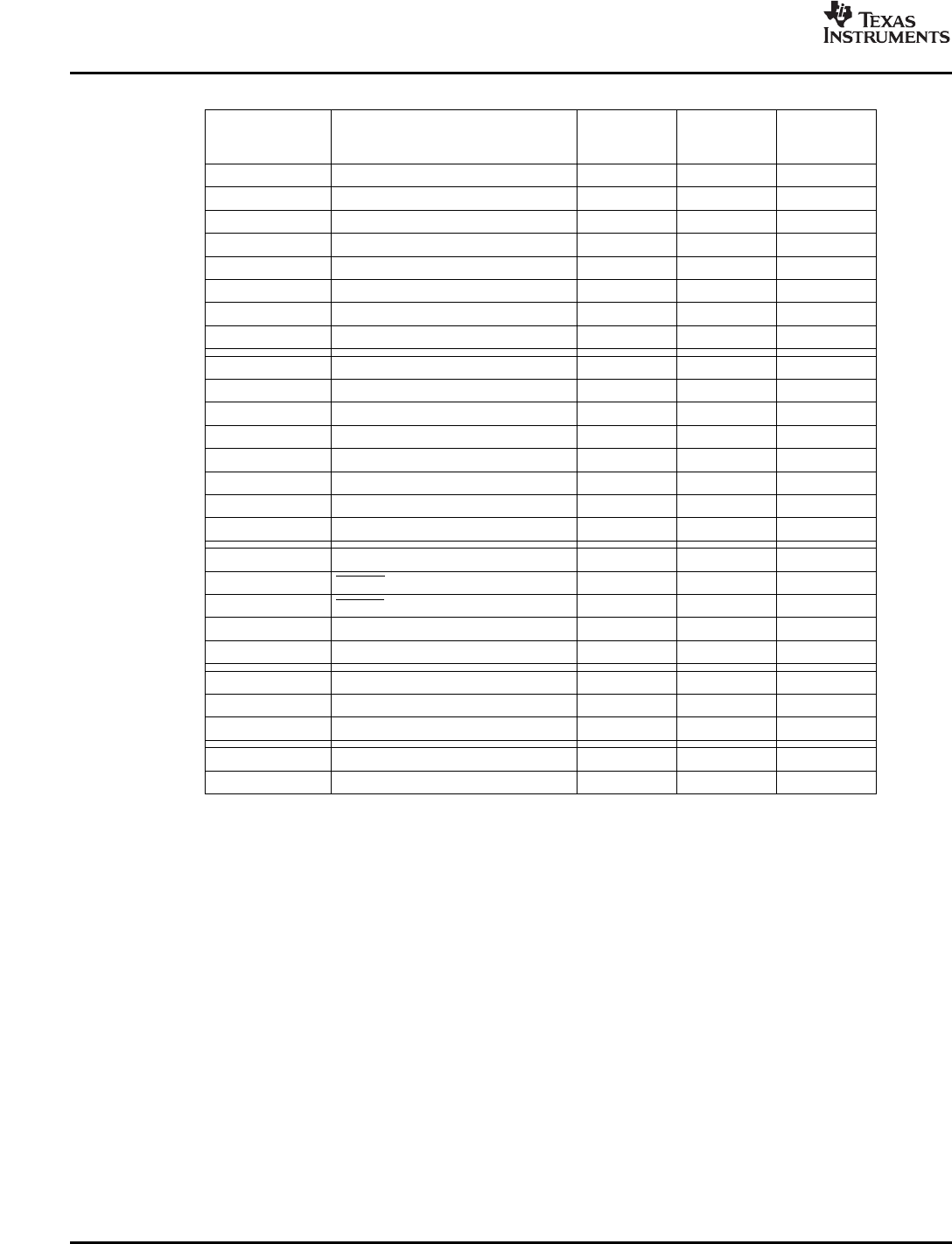

Table7-70.EMAC/MDIOMultiplexedPins(MII,RMII,andGMIIModes)

BALLNUMBERDEVICEPINNAMEMIIRMIIGMII

(MAC_SEL=(MAC_SEL=(MAC_SEL=

00b)01b)10b)

J2URDATA0/MRXD0/RMRXD0MRXD0RMRXD0MRXD0

H3URDATA1/MRXD1/RMRXD1MRXD1RMRXD1MRXD1

J1URDATA2/MRXD2MRXD2MRXD2

J3URDATA3/MRXD3MRXD3MRXD3

L1URDATA4/MRXD4MRXD4

L2URDATA5/MRXD5MRXD5

H2URDATA6/MRXD6MRXD6

M2URDATA7/MRXD7MRXD7

M1UXDATA0/MTXD0/RMTXD0MTXD0RMTXD0MTXD0

L4UXDATA1/MTXD1/RMTXD1MTXD1RMTXD1MTXD1

M4UXDATA2/MTXD2MTXD2MTXD2

K4UXDATA3/MTXD3MTXD3MTXD3

L3UXDATA4/MTXD4MTXD4

L5UXDATA5/MTXD5MTXD5

M3UXDATA6/MTXD6MTXD6

N5UXDATA7/MTXD7MTXD7

H4URSOC/MRXER/RMRXERMRXERRMRXERMRXER

H5URENB/MRXDVMRXDVMRXDV

J5UXENB/MTXEN/RMTXENMTXENRMTXENMTXEN

J4URCLAV/MCRS/RMCRSDVMCRSRMCRSDVMCRS

K3UXSOC/MCOLMCOLMCOL

K5UXCLAV/GMTCLKGMTCLK

H1URCLK/MRCLKMRCLKMRCLK

N4UXCLK/MTCLK/REFCLKMTCLKRMREFCLKMTCLK

N3UXADDR3/GMDIOMDIOMDIOMDIO

M5UXADDR4/GMDCLKMDCLKMDCLKMDCLK

UsingtheRMIIModeoftheEMAC

TheEthernetMediaAccessController(EMAC)containslogicthatallowsittocommunicateusingthe

ReducedMediaIndependentInterface(RMII)protocol.Thislogicmustbetakenoutofresetbeforebeing

used.TousetheRMIImodeoftheEMACfollowthesesteps:

1.EnabletheEMAC/MDIOthroughtheDeviceStateControlRegisters.

–UnlockthePERCFG0registerbywriting0x0F0A0B00tothePERLOCKregister.

–Setbit4inthePERCFG0registerwithin16SYSCLK3clockcyclestoenabletheEMAC/MDIO.

–PollthePERSTAT0registertoverifystatechange.

2.InitializetheEMAC/MDIOasneeded.

3.ReleasetheRMIIlogicfromresetbyclearingtheRMII_RSTbitoftheEMACConfigurationRegister

(seeSection3.4.5).

Asdescribedintheprevioussection,theRMIImodeoftheEMACmustbeselectedbysetting

MACSEL[1:0]=01batdevicereset.

C64x+PeripheralInformationandElectricalSpecifications 202SubmitDocumentationFeedback