www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

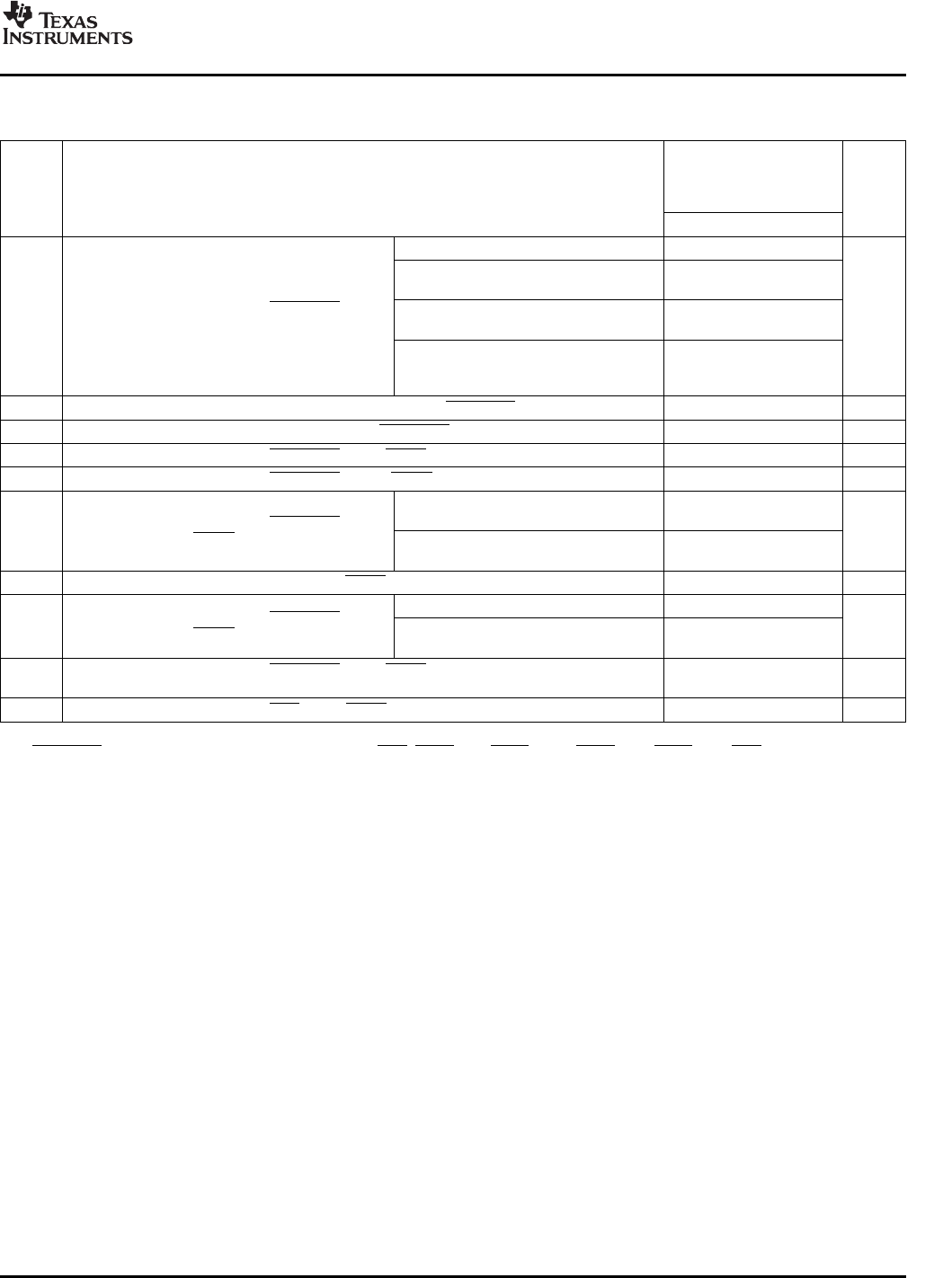

Table7-56.SwitchingCharacteristicsforHost-PortInterfaceCycles

(1)(2)

(seeTable7-56throughFigure7-51)

-720

-850

A-1000/-1000

NO.PARAMETERUNIT

-1200

MINMAX

Case1.HPICorHPIAread515

Case2.HPIDreadwithno

9*M+20

auto-increment

(3)

Delaytime,HSTROBElowto

Case3.HPIDreadwithauto-increment

1t

d(HSTBL-HDV)

ns

9*M+20

DSPdatavalid

andreadFIFOinitiallyempty

(3)

Case4.HPIDreadwithauto-increment

anddatapreviouslyprefetchedintothe515

readFIFO

2t

dis(HSTBH-HDV)

Disabletime,HDhigh-impedancefromHSTROBEhigh14ns

3t

en(HSTBL-HD)

Enabletime,HDdrivenfromHSTROBElow315ns

4t

d(HSTBL-HRDYH)

Delaytime,HSTROBElowtoHRDYhigh12ns

5t

d(HSTBH-HRDYH)

Delaytime,HSTROBEhightoHRDYhigh12ns

Case1.HPIDreadwithno

10*M+20

auto-increment

(3)

Delaytime,HSTROBElowto

6t

d(HSTBL-HRDYL)

ns

HRDYlow

Case2.HPIDreadwithauto-increment

10*M+20

andreadFIFOinitiallyempty

(3)

7t

d(HDV-HRDYL)

Delaytime,HDvalidtoHRDYlow0ns

Case1.HPIAwrite

(3)

5*M+20

Delaytime,HSTROBEhighto

34t

d(DSH-HRDYL)

ns

Case2.HPIDwritewithno

HRDYlow

5*M+20

auto-increment

(3)

Delaytime,HSTROBElowtoHRDYlowforHPIAwriteandFIFOnot

35t

d(HSTBL-HRDYL)

40*M+20ns

empty

(3)

36t

d(HASL-HRDYH)

Delaytime,HASlowtoHRDYhigh12ns

(1)M=SYSCLK3period=6/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useM=6ns.

(2)HSTROBEreferstothefollowinglogicaloperationonHCS,HDS1,andHDS2:[NOT(HDS1XORHDS2)]ORHCS.

(3)AssumestheHPIisaccessingL2/L1memoryandnoothermasterisaccessingthesamememorylocation.

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications181