www.ti.com

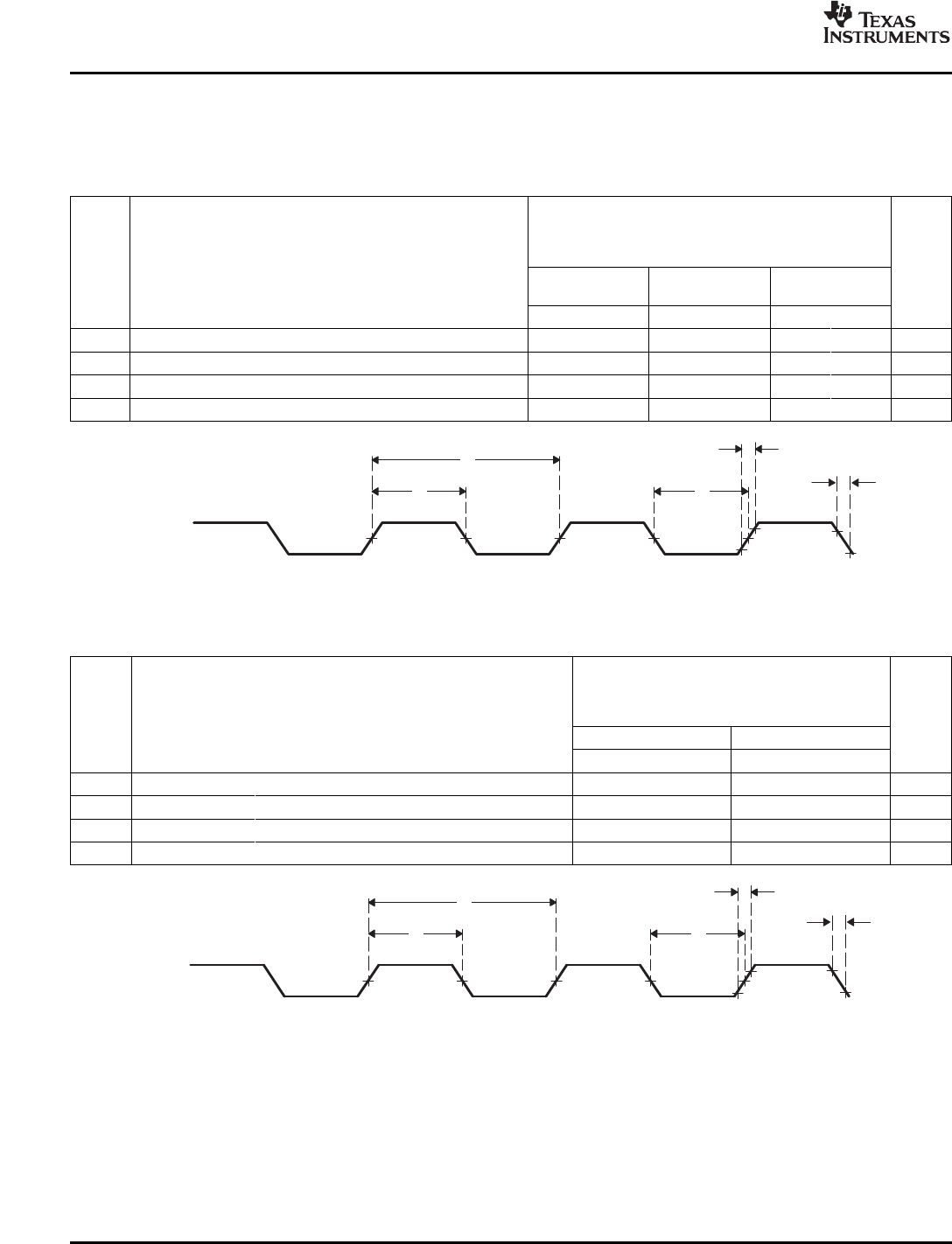

7.14.3EMACElectricalData/Timing

7.14.3.1EMACMIIandGMIIElectricalData/Timing

MRCLK

(Input)

2 3

1

4

4

MTCLK

(Input)

2 3

1

4

4

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

Table7-75.TimingRequirementsforMRCLK-MIIandGMIIOperation(seeFigure7-59)

-720

-850

A-1000/-1000

-1200

NO.UNIT

1000Mbps

100Mbps10Mbps

(GMIIOnly)

MINMAXMINMAXMINMAX

1t

c(MRCLK)

Cycletime,MRCLK840400ns

2t

w(MRCLKH)

Pulseduration,MRCLKhigh2.814140ns

3t

w(MRCLKL)

Pulseduration,MRCLKlow2.814140ns

4t

t(MRCLK)

Transitiontime,MRCLK133ns

Figure7-59.MRCLKTiming(EMAC–Receive)[MIIandGMIIOperation]

Table7-76.TimingRequirementsforMTCLK-MIIandGMIIOperation(seeFigure7-60)

-720

-850

A-1000/-1000

NO.UNIT

-1200

100Mbps10Mbps

MINMAXMINMAX

1t

c(MTCLK)

Cycletime,MTCLK40400ns

2t

w(MTCLKH)

Pulseduration,MTCLKhigh14140ns

3t

w(MTCLKL)

Pulseduration,MTCLKlow14140ns

4t

t(MTCLK)

Transitiontime,MTCLK33ns

Figure7-60.MTCLKTiming(EMAC–Transmit)[MIIandGMIIOperation]

C64x+PeripheralInformationandElectricalSpecifications 208SubmitDocumentationFeedback