www.ti.com

7.20SerialRapidIO(SRIO)Port

7.20.1SerialRapidIODevice-SpecificInformation

7.20.2SerialRapidIOPeripheralRegisterDescription(s)

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

TheSRIOportontheC6455deviceisahigh-performance,lowpin-countinterconnectaimedfor

embeddedmarkets.TheuseoftheRapidI/Ointerconnectinabasebandboarddesigncancreatea

homogeneousinterconnectenvironment,providingevenmoreconnectivityandcontrolamongthe

components.RapidI/Oisbasedonthememoryanddeviceaddressingconceptsofprocessorbuses

wherethetransactionprocessingismanagedcompletelybyhardware.ThisenablestheRapidI/O

interconnecttolowerthesystemcostbyprovidinglowerlatency,reducedoverheadofpacketdata

processing,andhighersystembandwidth,allofwhicharekeyforwirelessinterfaces.TheRapidI/O

interconnectoffersverylowpin-countinterfaceswithscalablesystembandwidthbasedon10-Gigabitper

second(Gbps)bidirectionallinks.

ThePHYpartoftheRIOconsistsofthephysicallayerandincludestheinputandoutputbuffers(each

seriallinkconsistsofadifferentialpair),the8bit/10bitencoder/decoder,thePLLclockrecovery,andthe

parallel-to-serial/serial-to-parallelconverters.

TheRapidIOinterfaceshouldbedesignedtooperateatadatarateof3125Gbpsperdifferentialpair.

Thisequals12.5rawGBaud/sforthe4xRapidIOport,orapproximately9Gbpsdatathroughputrate.

TheapproachtospecifyinginterfacetimingfortheSRIOPortisdifferentthanonotherinterfacessuchas

EMIF,HPI,andMcBSP.Fortheseotherinterfacesthedevicetimingwasspecifiedintermsofdata

manualspecificationsandI/Obufferinformationspecification(IBIS)models.

FortheC6455SRIOPort,TexasInstruments(TI)providesaprintedcircuitboard(PCB)solutionshowing

twoDSPsconnectedviaa4xSRIOlinkdirectlytotheuser.TIhasperformedthesimulationandsystem

characterizationtoensureallSRIOinterfacetimingsinthissolutionaremet.ThecompleteSRIOsystem

solutionisdocumentedintheImplementingSerialRapidI/OPCBLayoutonaTMS320C6455Hardware

Designapplicationreport(literaturenumberSPRAAA8).

TIonlysupportsdesignsthatfollowtheboarddesignguidelinesoutlinedintheSPRAAA8

applicationreport.

TheSerialRapidIOperipheralisamasterperipheralintheC6455DSP.ItconformstotheRapidIO™

InterconnectSpecification,PartVI:PhysicalLayer1x/4xLP-SerialSpecification,Revision1.2.

IftheSRIOperipheralisnotused,theSRIOreferenceclockinputsandSRIOlinkpinscanbeleft

unconnected.IftheSRIOperipheralisenabledbutnotalllinksareused,thepinsoftheunusedlinkscan

beleftunconnectedandnoterminationsareneeded.Formoreinformation,seetheTMS320C6455

DesignGuideandComparisonstoTMS320TC6416T(literaturenumberSPRAA89).

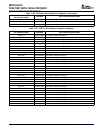

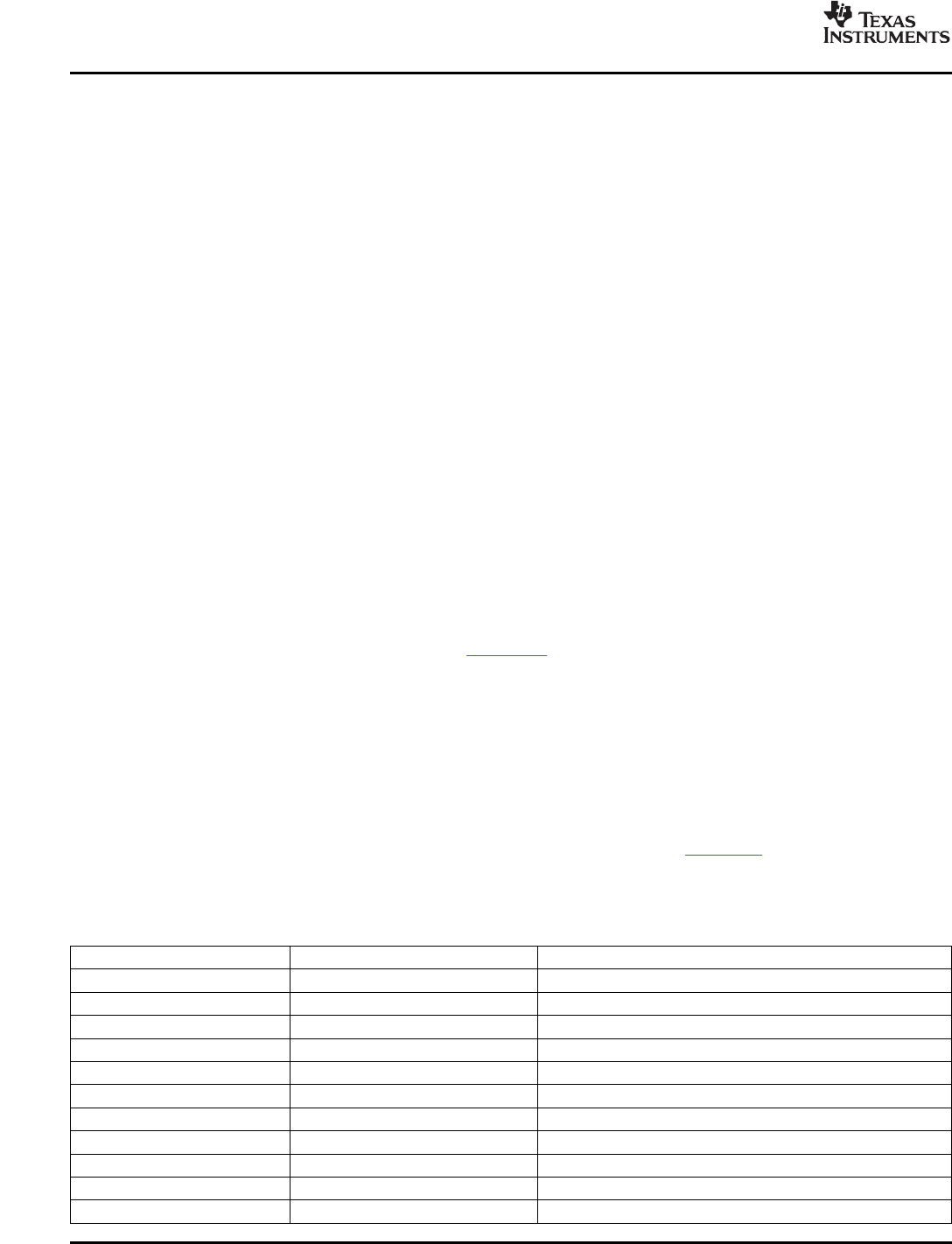

Table7-112.RapidIOControlRegisters

HEXADDRESSRANGEACRONYMREGISTERNAME

02D00000RIO_PIDPeripheralIdentificationRegister

02D00004RIO_PCRPeripheralControlRegister

02D00008-02D0001C-Reserved

02D00020RIO_PER_SET_CNTLPeripheralSettingsControlRegister

02D00024-02D0002C-Reserved

02D00030RIO_GBL_ENPeripheralGlobalEnableRegister

02D00034RIO_GBL_EN_STATPeripheralGlobalEnableStatus

02D00038RIO_BLK0_ENBlockEnable0

02D0003CRIO_BLK0_EN_STATBlockEnableStatus0

02D00040RIO_BLK1_ENBlockEnable1

02D00044RIO_BLK1_EN_STATBlockEnableStatus1

C64x+PeripheralInformationandElectricalSpecifications 234SubmitDocumentationFeedback