www.ti.com

7.7.3.4PLLControllerDivider4Register

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

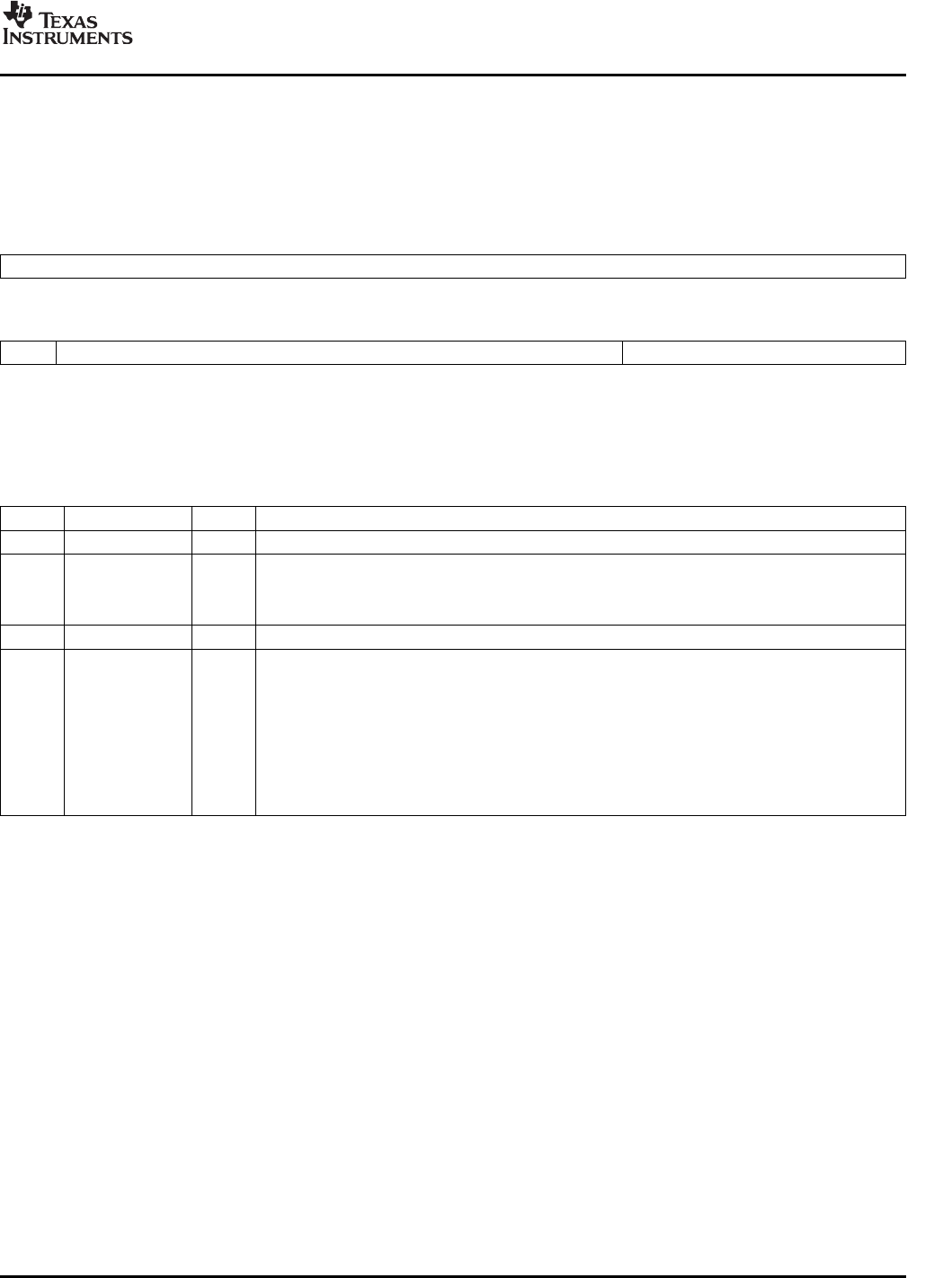

ThePLLcontrollerdivider4register(PLLDIV4)isshowninFigure7-14anddescribedinTable7-22.

BesidesbeingusedastheEMIFAinternalclock,SYSCLK4isalsousedinotherpartsofthesystem.

Disablingthisclockwillcauseunpredictablesystembehavior.Therefore,thePLLDIV4registershould

neverbeusedtodisableSYSCLK4.

3116

Reserved

R-0

1514540

D4ENReservedRATIO

R/W-1R-0R/W-3

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Figure7-14.PLLControllerDivider4Register(PLLDIV4)[HexAddress:029A0160]

Table7-22.PLLControllerDivider4Register(PLLDIV4)FieldDescriptions

BitFieldValueDescription

31:16Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

15D4ENDivider4enablebit.

0Divider4isdisabled.Noclockoutput.

1Divider4isenabled.

14:5Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

4:0RATIO0-1FhDividerratiobits.

0÷2.Dividefrequencyby2.

1h÷4.Dividefrequencyby4.

2h÷6.Dividefrequencyby6.

3h÷8.Dividefrequencyby8.

4h-7h÷10to÷16.Dividefrequencyby10todividefrequencyby16.

8h-1FhReserved,donotuse.

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications143