www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

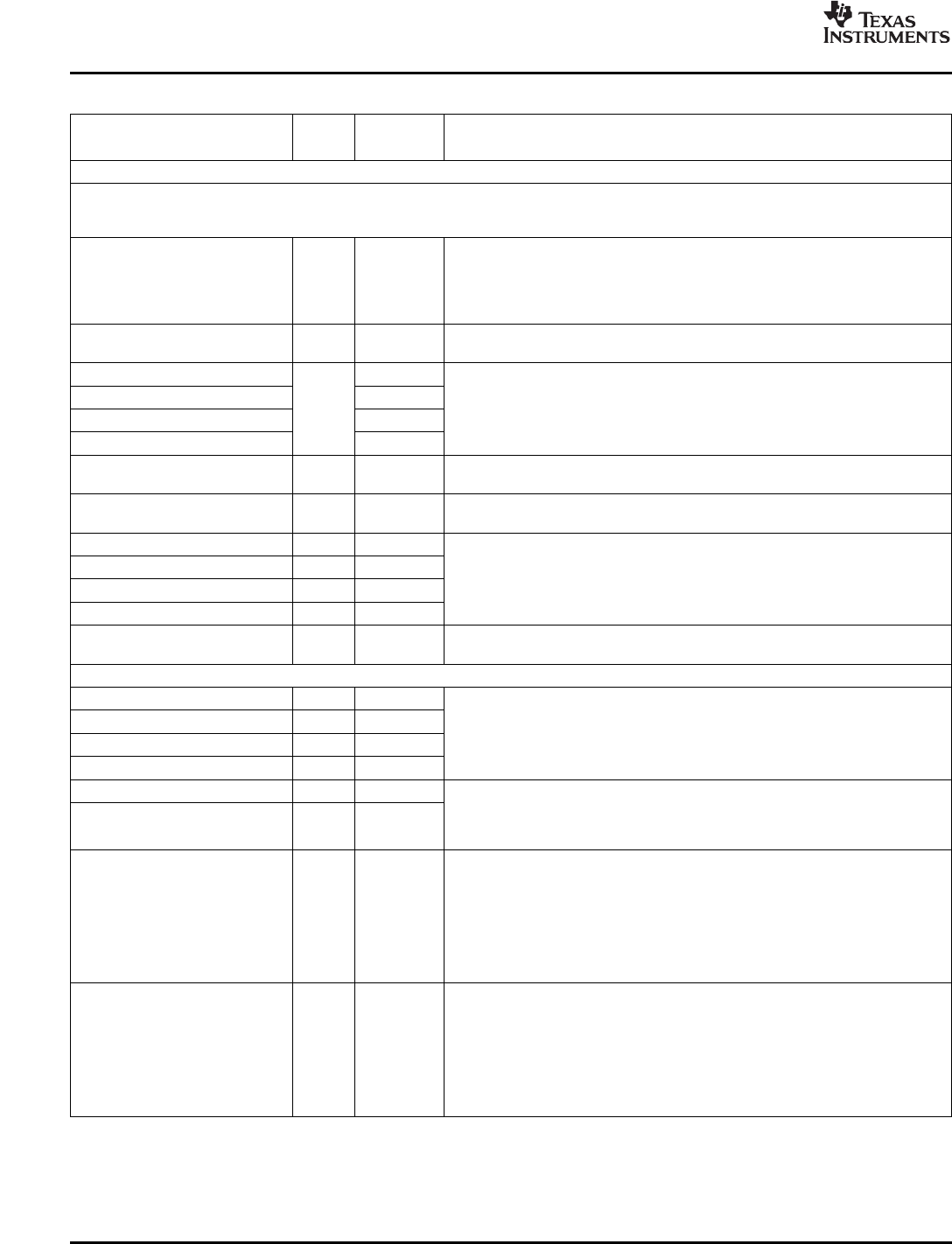

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

ETHERNETMAC(EMAC)[RGMII]

IftheEthernetMAC(EMAC)andMDIOareenabled(AEA12drivenlow[UTOPIA_EN=0]),therearetwoadditionalconfigurationpins—

theMAC_SEL[1:0](AEA[10:9]pins)thatselectoneofthefourinterfacemodes(MII,RMII,GMII,orRGMII)fortheEMAC/MDIOinterface.

FormoredetailedinformationontheEMACconfigurationpins,seeSection3,DeviceConfiguration.

RGMIIreferenceclock(O).This125-MHzreferenceclockisprovidedasa

convenience.ItcanbeusedasaclocksourcetoaPHY,sothatthePHYmay

RGREFCLKC4O/ZgenerateRXCclocktocommunicatewiththeEMAC.Thisclockisstopped

whilethedeviceisinreset.ThispinisavailableonlywhenRGMIImodeis

selected(MACSEL[1:0]=11).

RGMIItransmitclock(O).ThispinisavailableonlywhenRGMIImodeis

RGTXCD4O/Z

selected(MACSEL[1:0]=11).

RGTXD3A2

RGTXD2C3

RGMIItransmitdata[3:0](O).ThispinisavailableonlywhenRGMIImodeis

O/Z

selected(MACSEL[1:0]=11).

RGTXD1B3

RGTXD0A3

RGMIItransmitenable(O).ThispinisavailableonlywhenRGMIImodeis

RGTXCTLD3O/Z

selected(MACSEL[1:0]=11).

RGMIIreceiveclock(I).ThispinisavailableonlywhenRGMIImodeisselected

RGRXCE3I

(MACSEL[1:0]=11).

RGRXD3C1I

RGRXD2E4I

RGMIIreceivedata[3:0](I).ThispinisavailableonlywhenRGMIImodeis

selected(MACSEL[1:0]=11).

RGRXD1E2I

RGRXD0E1I

RGMIIreceivecontrol(I).ThispinisavailableonlywhenRGMIImodeis

RGRXCTLC2I

selected(MACSEL[1:0]=11).

RESERVEDFORTEST

RSV02V5

RSV03W3

Reserved.Thesepinsmustbeconnecteddirectlytocoresupply(CV

DD

)for

properdeviceoperation.

RSV04N11

RSV05P11

RSV07G4IReserved.Thesepinsmustbeconnecteddirectlyto1.5-/1.8-VI/Osupply

(DV

DD15

)forproperdeviceoperation.

NOTE:IftheEMACRGMIIisnotused,thesepinscanbeconnecteddirectlyto

RSV09D26I

ground(V

SS

).

Reserved.Thispinmustbeconnectedtoground(V

SS

)viaa200-Ωresistorfor

properdeviceoperation.

NOTE:IftheDDR2MemoryControllerisnotused,theV

REFSSTL

,RSV11,and

RSV12pinscanbeconnecteddirectlytoground(V

SS

)tosavepower.

RSV11D24

However,connectingthesepinsdirectlytogroundwillpreventboundary-scan

fromfunctioningontheDDR2MemoryControllerpins.Topreserve

boundary-scanfunctionalityontheDDR2MemoryControllerpins,see

Section7.3.4.

Reserved.Thispinmustbeconnectedtothe1.8-VI/Osupply(DV

DD18

)viaa

200-Ωresistorforproperdeviceoperation.

NOTE:IftheDDR2MemoryControllerisnotused,theV

REFSSTL

,RSV11,and

RSV12pinscanbeconnecteddirectlytoground(V

SS

)tosavepower.

RSV12C24

However,connectingthesepinsdirectlytogroundwillpreventboundary-scan

fromfunctioningontheDDR2MemoryControllerpins.Topreserve

boundary-scanfunctionalityontheDDR2MemoryControllerpins,see

Section7.3.4.

DeviceOverview 44SubmitDocumentationFeedback