www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

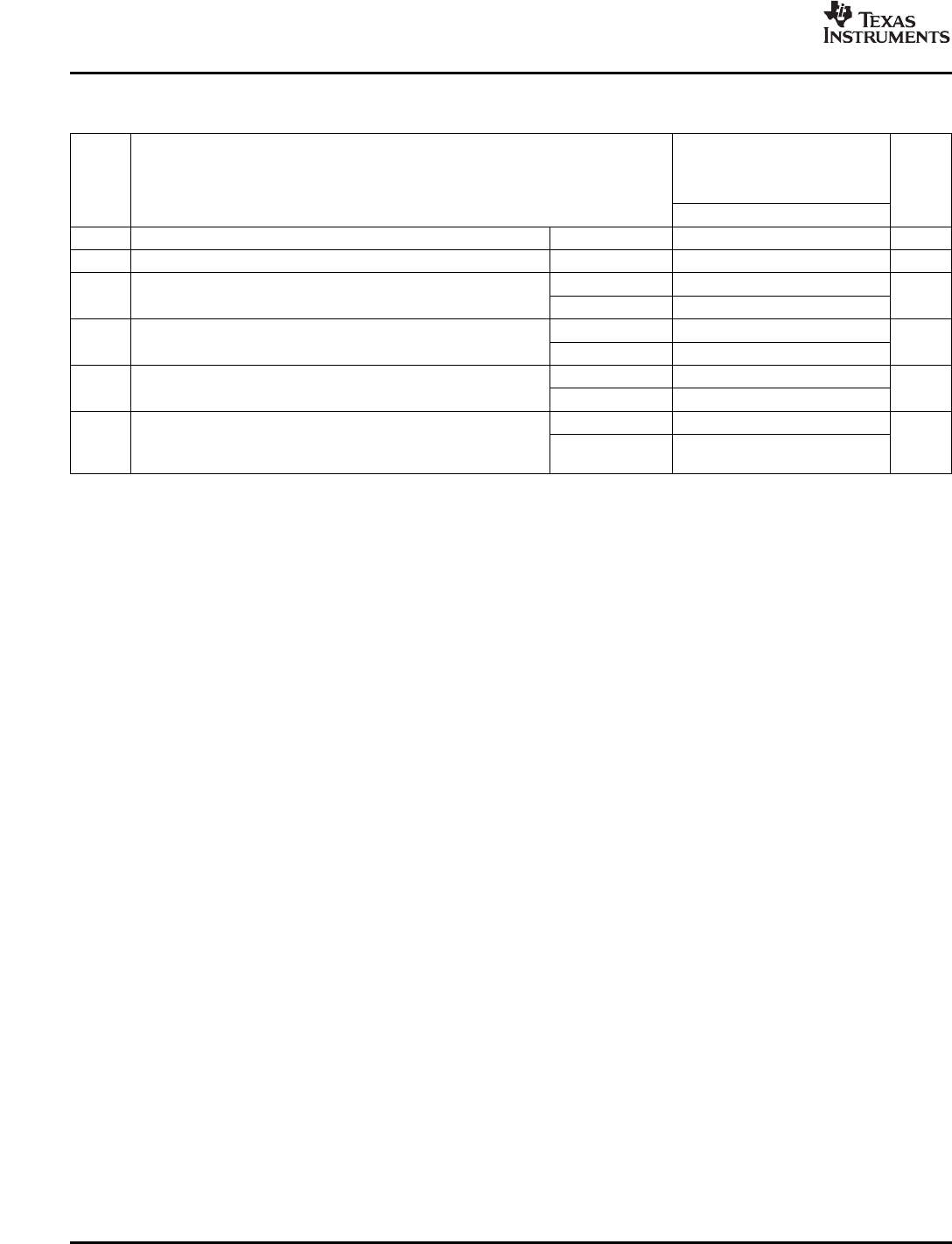

Table7-60.SwitchingCharacteristicsOverRecommendedOperatingConditionsforMcBSP

(seeFigure7-52)(continued)

-720

-850

A-1000/-1000

NO.PARAMETERUNIT

-1200

MINMAX

3t

w(CKRX)

Pulseduration,CLKR/XhighorCLKR/XlowCLKR/XintC–1

(7)

C+1

(7)

ns

4t

d(CKRH-FRV)

Delaytime,CLKRhightointernalFSRvalidCLKRint–2.13.3ns

CLKXint–1.73

9t

d(CKXH-FXV)

Delaytime,CLKXhightointernalFSXvalidns

CLKXext1.79

CLKXint–3.94

Disabletime,DXhighimpedancefollowing

12t

dis(CKXH-DXHZ)

ns

lastdatabitfromCLKXhigh

CLKXext2.19

CLKXint–3.9+D1

(8)

4+D2

(8)

13t

d(CKXH-DXV)

Delaytime,CLKXhightoDXvalidns

CLKXext2.1+D1

(8)

9+D2

(8)

Delaytime,FSXhightoDXvalidFSXint–2.3+D1

(9)

5.6+D2

(9)

14t

d(FXH-DXV)

ns

ONLYapplieswhenindata

FSXext1.9+D1

(9)

9+D2

(9)

delay0(XDATDLY=00b)mode

(7)C=HorL

S=samplerategeneratorinputclock=6PifCLKSM=1(P=1/CPUclockfrequency)

S=samplerategeneratorinputclock=P_clksifCLKSM=0(P_clks=CLKSperiod)

H=CLKXhighpulsewidth=(CLKGDV/2+1)*SifCLKGDViseven

H=(CLKGDV+1)/2*SifCLKGDVisodd

L=CLKXlowpulsewidth=(CLKGDV/2)*SifCLKGDViseven

L=(CLKGDV+1)/2*SifCLKGDVisodd

CLKGDVshouldbesetappropriatelytoensuretheMcBSPbitratedoesnotexceedthemaximumlimit(see(4)above).

(8)ExtradelayfromCLKXhightoDXvalidappliesonlytothefirstdatabitofadevice,ifandonlyifDXENA=1inSPCR.

ifDXENA=0,thenD1=D2=0

ifDXENA=1,thenD1=6P,D2=12P

(9)ExtradelayfromFSXhightoDXvalidappliesonlytothefirstdatabitofadevice,ifandonlyifDXENA=1inSPCR.

ifDXENA=0,thenD1=D2=0

ifDXENA=1,thenD1=6P,D2=12P

C64x+PeripheralInformationandElectricalSpecifications 194SubmitDocumentationFeedback