www.ti.com

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

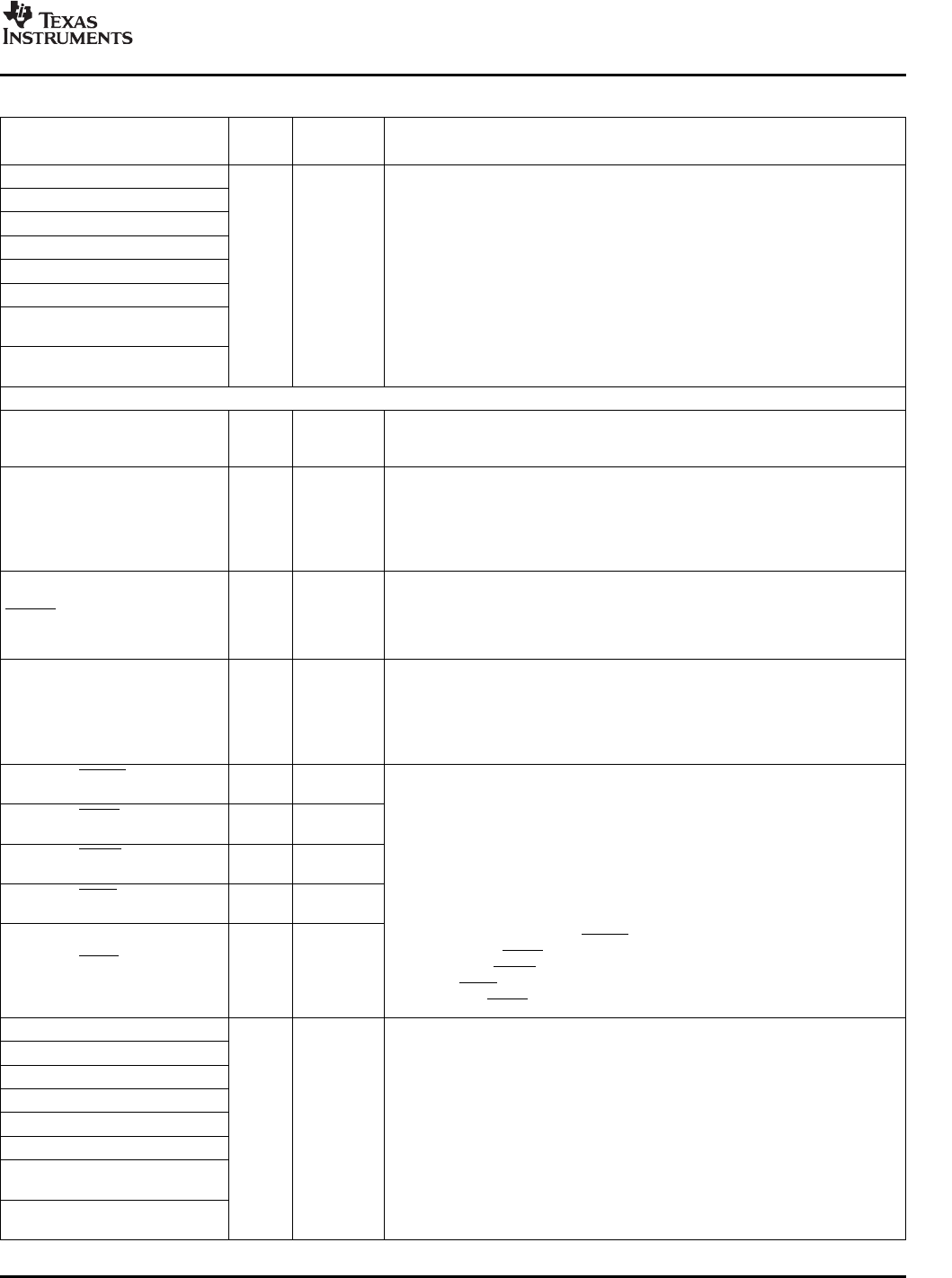

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

UXDATA7/MTXD7N5

UXDATA6/MTXD6M3UTOPIA8bittransmitdatabus(I/O/Z)[default]orEMACMII4bittransmitdata

bus(I/O/Z)[default]orEMACGMII8bittransmitdatabusorEMACRMII2bit

UXDATA5/MTXD5L5

transmitdatabus(I/O/Z)

UXDATA4/MTXD4L3

UsingtheTransmitDataBus,theUTOPIASlave(ontherisingedgeofthe

UXDATA3/MTXD3K4

O/ZUXCLK)transmitsthe8bitATMcellstotheMasterATMController.

UXDATA2/MTXD2M4

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),these

UXDATA1/MTXD1/pinsfunctionasEMACpinsandarecontrolledbytheMACSEL[1:0](AEA[10:9]

L4

RMTXD1pins)toselecttheMII,RMII,GMIIorRGMIIEMACinterface.(Formoredetails,

seeSection3,DeviceConfiguration).

UXDATA0/MTXD0/

M1

RMTXD0

UTOPIASLAVE(ATMCONTROLLER)-RECEIVEINTERFACE

SourceclockforUTOPIAreceivedrivenbyMasterATMController.

URCLK/MRCLKH1I/O/ZWhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACMII[default]orGMIIreceiveclock.MACSEL[1:0]dependent.

ReceivecellavailablestatusoutputsignalfromUTOPIASlave.

0indicatesNOspaceisavailabletoreceiveacellfromMasterATMController

URCLAV/MCRS/1indicatesspaceisavailabletoreceiveacellfromMasterATMController

J4I/O/Z

RMCRSDVWhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACMIIcarriersense[default]orRMIIcarriersense/datavalidorGMII

carriersense.MACSEL[1:0]dependent.MACSEL[1:0]dependent.

UTOPIAreceiveinterfaceenableinputsignal.AssertedbytheMasterATM

ControllertoindicatetotheUTOPIASlavetosampletheReceiveDataBus

URENB/MRXDVH5I/O/Z(URDATA[7:0])andURSOCsignalinthenextclockcycleorthereafter.

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACMII[default]orGMIIreceivedatavalid.MACSEL[1:0]dependent.

ReceiveStart-of-Cellsignal.ThissignalisoutputbytheMasterATMController

toindicatetotheUTOPIASlavethatthefirstvalidbyteofthecellisavailableto

URSOC/MRXER/sampleonthe8bitReceiveDataBus(URDATA[7:0]).

H4I/O/Z

RMRXERWhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),this

pinisEMACMII[default]orRMIIorGMIIreceiveerror.MACSEL[1:0]

dependent.

URADDR4/PCBE0/UTOPIAreceiveaddresspins[URADDR[4:0](I)]:

P1I

GP[2]AsUTOPIAreceiveaddresspins,UTOPIA_EN(AEA12pin)=1:

•5bitSlavereceiveaddressinputpinsdrivenbytheMasterATMController

URADDR3/PREQ/

P2I

toidentifyandselectoneoftheSlavedevices(upto31possible)inthe

GP[15]

ATMSystem.

URADDR2/PINTA

(1)

/

P3I

•WhentheUTOPIAperipheralisdisabled[UTOPIA_EN(AEA12pin)=0],

GP[14]

thesepinsarePCI(ifPCI_EN=1)orGPIO(ifPCI_EN=0)pins

URADDR1/PRST/

(GP[15:12,2]).

R5I

GP[13]

AsPCIperipheralpins:

PCIcommand/byteenable0(PCBE0)[I/O/Z]

PCIbusrequest(PREQ)[O/Z],

URADDR0/PGNT/

R4I

PCIinterruptA(PINTA)[O/Z],

GP[12]

PCIreset(PRST)[I],and

PCIbusgrant(PGNT)[I/O/Z].

URDATA7/MRXD7M2

URDATA6/MRXD6H2

UTOPIA8bitReceiveDataBus(I/O/Z)[default]orEMACreceivedatabus

URDATA5/MRXD5L2

[MII][default](I/O/Z)or[GMII](I/O/Z)or[RMII](I/O/Z)

UsingtheReceiveDataBus,theUTOPIASlave(ontherisingedgeofthe

URDATA4/MRXD4L1

URCLK)canreceivethe8bitATMcelldatafromtheMasterATMController.

URDATA3/MRXD3J3

I/O/Z

WhentheUTOPIAperipheralisdisabled(UTOPIA_EN[AEA12pin]=0),these

URDATA2/MRXD2J1

pinsfunctionasEMACpinsandarecontrolledbytheMACSEL[1:0](AEA[10:9]

URDATA1/MRXD1/

pins)toselecttheMII,RMII,GMII,orRGMIIEMACinterface.(Formoredetails,

H3

RMRXD1

seeSection3,DeviceConfiguration).

URDATA0/MRXD0/

J2

RMRXD0

(1)Thesepinsfunctionasopen-drainoutputswhenconfiguredasPCIpins.

SubmitDocumentationFeedbackDeviceOverview41