www.ti.com

3.2PeripheralConfigurationatDeviceReset

SM320C6455-EP

FIXED-POINTDIGITALSIGNALPROCESSOR

SPRS462B–SEPTEMBER2007–REVISEDJANUARY2008

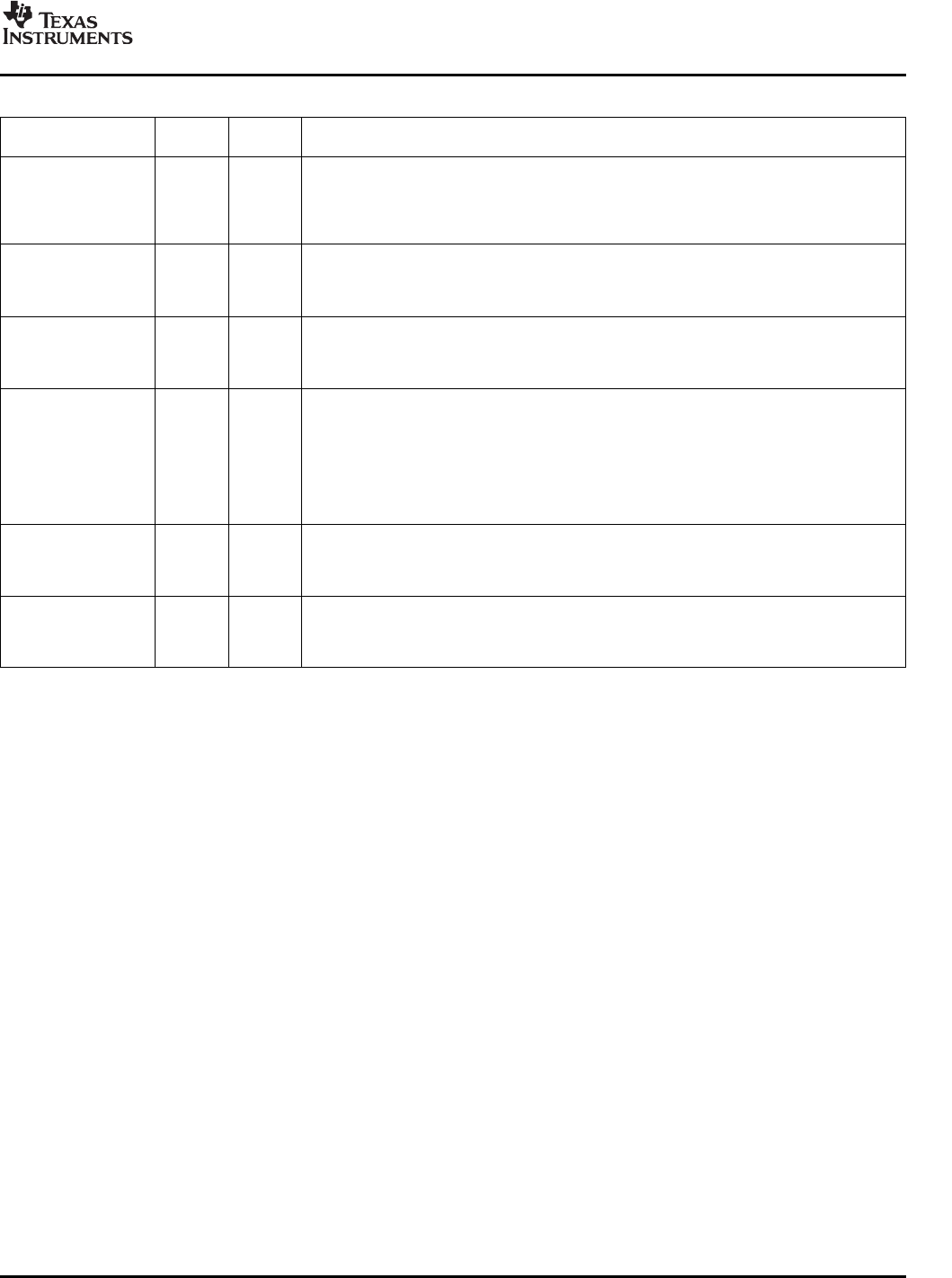

Table3-1.C6455DeviceConfigurationPins(AEA[19:0],ABA[1:0],andPCI_EN)(continued)

CONFIGURATIONIPD/

NO.FUNCTIONALDESCRIPTION

PINIPU

(1)

SYSCLKOUTEnablebit(SYSCLKOUT_EN).

SelectswhichfunctionisenabledontheSYSCLK4/GP[1]muxedpin.

AEA4T28IPD

0GP[1]pinfunctionisenabled(default)

1SYSCLK4pinfunctionisenabled

ForproperC6455deviceoperation,theAEA3pinmustbepulledupatdeviceresetusinga

1-kΩresistorifpowerisappliedtotheSRIOsupplypins.IftheSRIOperipheralisnotused

AEA3T27IPD

andtheSRIOsupplypinsareconnectedtoV

SS

,theAEA3pinmustbepulleddowntoV

SS

usinga1-kΩresistor.

ConfigurationGeneral-PurposeInputs(CFGGP[2:0])

[T26,

ThevalueofthesepinsislatchedtotheDeviceStatusRegisterfollowingdeviceresetandis

AEA[2:0]U26,IPD

usedbytheon-chipbootloaderforsomebootmodes.Formoreinformationontheboot

U25]

modes,seeSection2.4,BootSequence.

PCIpinfunctionenablebit(PCI_EN).

SelectswhichfunctionisenabledontheHPI/PCIandthePCI/UTOPIAmultiplexedpins.

0HPIandUTOPIApinfunctionenabled(default)

PCI_ENY29IPDThismeansallmultiplexedHPI/PCIandPCI/UTOPIApinsfunctionasHPIand

UTOPIApins,respectively.

1PCIpinfunctionenabled

ThismeansallmultiplexedHPI/PCIandPCI/UTOPIApinsfunctionasPCIpins.

DDR2MemoryControllerenable(DDR2_EN).

ABA0V26IPD0DDR2MemoryControllerperipheralpinsaredisabled(default)

1DDR2MemoryControllerperipheralpinsareenabled

EMIFAenable(EMIFA_EN).

ABA1V25IPD0EMIFAperipheralpinsaredisabled(default)

1EMIFAperipheralpinsareenabled

SomeC6455peripheralssharethesamepins(internallymultiplexed)andaremutuallyexclusive.

Therefore,notallperipheralsmaybeusedatthesametime.Thedeviceconfigurationpinsdescribedin

Section3.1,DeviceConfigurationatDeviceReset,determinewhichfunctionisenabledforthemultiplexed

pins.

Notethatwhenthepinfunctionofaperipheralisdisabledatdevicereset,theperipheralispermanently

disabledandcannotbeenableduntilitspinfunctionisenabledandanotherdeviceresetisexecuted.

Also,notethatenablingthepinfunctionofaperipheraldoesnotenablethecorrespondingperipheral.All

peripheralsontheC6455devicearedisabledbydefault,exceptwhenusedforboot,andmustbeenabled

throughsoftwarebeforebeingused.

OtherperipheraloptionslikePCIclockspeedandEMAC/MDIOinterfacemodecanalsobeselectedat

deviceresetthroughthedeviceconfigurationpins.Theconfigurationselectedisalsofixedatdevicereset

andcannotbechangeduntilanotherdeviceresetisexecutedwithadifferentconfigurationselected.

ThemultiplyfactorofthePLL1Controllerisnotselectedthroughtheconfigurationpins.ThePLL1multiply

factorissetinsoftwarethroughthePLL1controllerregistersafterdevicereset.ThePLL2multiplyfactoris

fixed.Formoreinformation,seeSection7.7,PLL1andPLL1Controller,andSection7.8,PLL2andPLL2

Controller.

OntheC6455device,thePCIperipheralpinsaremultiplexedwiththeHPIpinsandpartiallymultiplexed

withtheUTOPIApins.ThePCI_ENpinselectsthefunctionfortheHPI/PCImultiplexedpins.ThePCI66,

PCI_EEAI,andHPI_WIDTHcontrolotherfunctionsofthePCIandHPIperipherals.Table3-2describes

theeffectofthePCI_EN,PCI66,PCI_EEAI,andHPI_WIDTHconfigurationpins.

SubmitDocumentationFeedbackDeviceConfiguration61