106 21555 Non-Transparent PCI-to-PCI Bridge User Manual

Error Handling

12.1.2 Secondary PCI Bus Error Signals

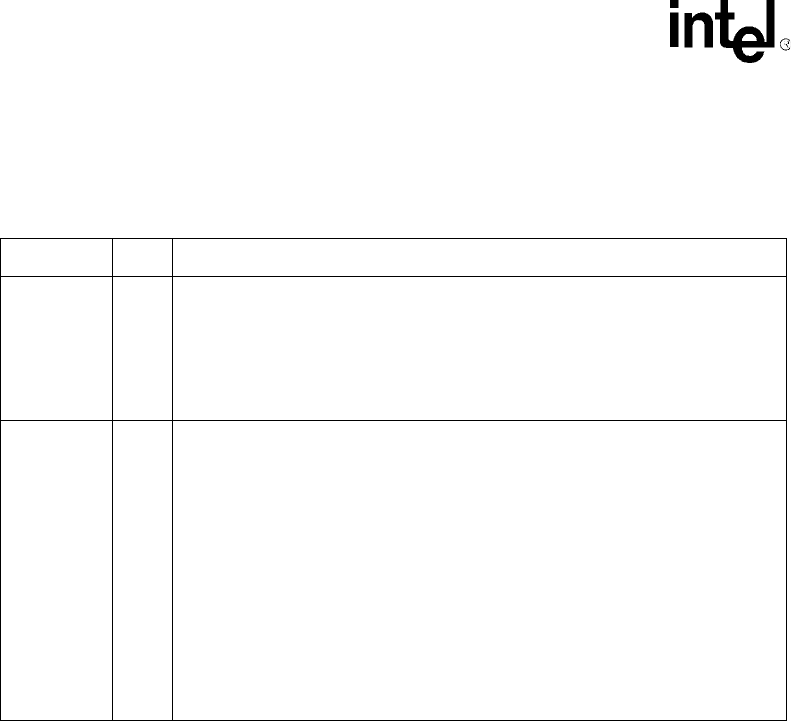

Table 28 describes the secondary PCI bus error signals.

Table 28. Secondary PCI Bus Arbitration Signals

Signal Name Type Description

s_perr_l STS

Secondary PCI interface PERR#. Signal s_perr_l is asserted when a data parity

error is detected for data received on the secondary interface. The timing of s_perr_l

corresponds to s_par driven one clock cycle earlier, and s_ad driven two clock cycles

earlier. Signal s_perr_l is asserted by the target during write transactions, and by the

initiator during read transactions.

Upon completion of a transaction, s_perr_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

s_serr_l OD

Secondary PCI interface SERR#. Signal s_serr_l can be driven low by any device on

the secondary bus to indicate a system error condition. The 21555 also samples

s_serr_l as an input and conditionally forwards it to the primary bus on p_serr_l. The

21555 can conditionally assert s_serr_l for the following reasons:

• Secondary bus address parity error.

• Upstream posted write data parity error on primary bus.

• Master abort during upstream posted write transaction.

• Target abort during upstream posted write transaction.

• Upstream posted write transaction discarded.

• Upstream delayed write request discarded.

• Upstream delayed read request discarded.

• Upstream delayed transaction master timeout.

Signal s_serr_l is pulled up through an external resistor.