132 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

3 Prefetchable R

Indicates if this space is prefetchable.

• When a 0, do not use prefetching when reading the 21555 registers.

11:4 — R Returns zero.

31:12

Base

Address

R/W

Indicate to configuration software the size of the requested memory address

range and set the base address of the range. The bits are mappable, and

indicates that the 21555 is requesting a 4Kb memory space.

a. The Secondary CSR Memory BARs map the 21555 registers into secondary bus memory space.

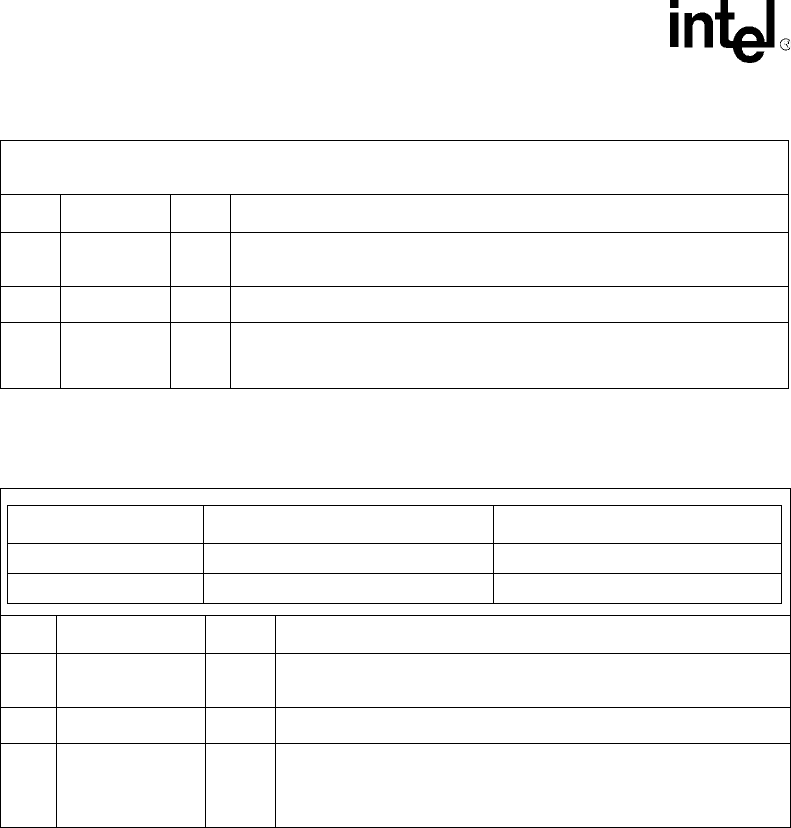

Table 36. Primary and Secondary CSR I/O Bars

a

a. The Primary and Secondary CSR I/O BARs map the 21555 registers into primary and secondary

I/O space, respectively.

Bit Name R/W Description

0 Space Indicator R

Indicates the type of address space that is requested.

When a one (1), I/O space is requested.

7:1 Reserved R Returns 0.

31:8 Base Address R/W

Indicates to configuration software the size of the requested I/O

address range and set the base address of the range. The bits are

mappable, and indicates that the 21555 is requesting a 256 byte I/O

space.

Table 35. Secondary CSR Memory BARs

a

(Sheet 2 of 2)

• Primary byte offset: 53:50h

• Secondary byte offset: 13:10h

Bit Name R/W Description

Offsets Primary CSR I/O BAR Secondary CSR I/O BAR

Primary byte 17:14h 57:54h

Secondary byte 57:54h 17:14h