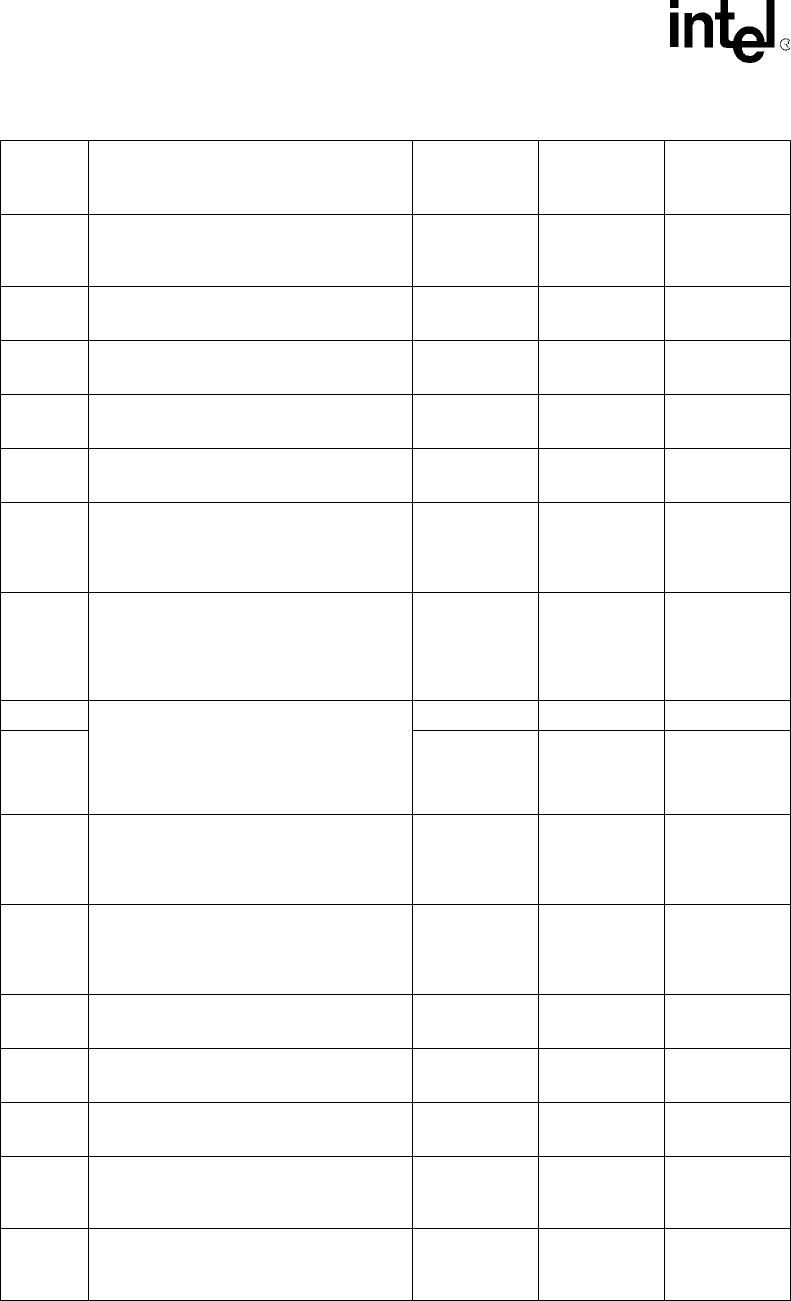

128 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

057:054

I2O Outbound Post_List Head Pointer,

page 167

I20 Outbound Post Head Pointer

Indeterminate Y Y

05B:058

I2O Inbound Post_List Counter, page 168

I20 Inbound Post Counter

00000000 Secondary Y

05F:05C

I2O Inbound Free_List Counter, page 168

I20 Inbound Free Counter

00000000 Secondary Y

063:060

I2O Outbound Post_List Counter, page 169

I20 Outbound Post Counter

00000000 Secondary Y

067:064

I2O Outbound Post_List Counter, page 169

I20 Outbound Free Counter

00000000 Secondary Y

06B:068

Downstream Memory 0, 2, 3, and Upstream

Memory 1 Translated Base Register, page

137

Downstream Memory 0 Translated Base

Indeterminate Y Y

06F:06C

Downstream I/O or Memory 1 and

Upstream I/O or Memory 0 Translated Base

Register, page 136

Downstream I/O or Memory 1 Translated

Base

Indeterminate Y Y

073:070 Downstream Memory 0, 2, 3, and Upstream

Memory 1 Translated Base Register, page

137

Downstream Memory 2 Translated Base

Downstream Memory 3 Translated Base

Indeterminate Y Y

077:074 Indeterminate Y Y

07B:078

Downstream I/O or Memory 1 and

Upstream I/O or Memory 0 Translated Base

Register, page 136

Upstream I/O or Memory 0 Translated Base

Indeterminate Y Y

07F:07C

Downstream Memory 0, 2, 3, and Upstream

Memory 1 Translated Base Register, page

137

Upstream Memory 1 Translated Base

Indeterminate Y Y

083:082

Chip Status CSR, page 170

Chip Status CSR

0000 W1TC Y

085:084

Chip Set IRQ Mask Register, page 170

Chip Set IRQ Mask

FFFF W1TS Y

087:086

Chip Clear IRQ Mask Register, page 171

Chip Clear IRQ Mask

FFFF W1TC Y

08B:088

Upstream Page Boundary IRQ 0 Register,

page 171

Upstream Page Boundary IRQ 0

00000000 W1TC Y

08F:08C

Upstream Page Boundary IRQ 1 Register,

page 172

Upstream Page Boundary IRQ 1

00000000 W1TC Y

Table 33. CSR Address Map (Sheet 3 of 5)

Byte

Offset

(Hex)

Register Name Reset Value Write Access Read Access