78 21555 Non-Transparent PCI-to-PCI Bridge User Manual

Clocking

7.2 21555 Secondary Clock Outputs

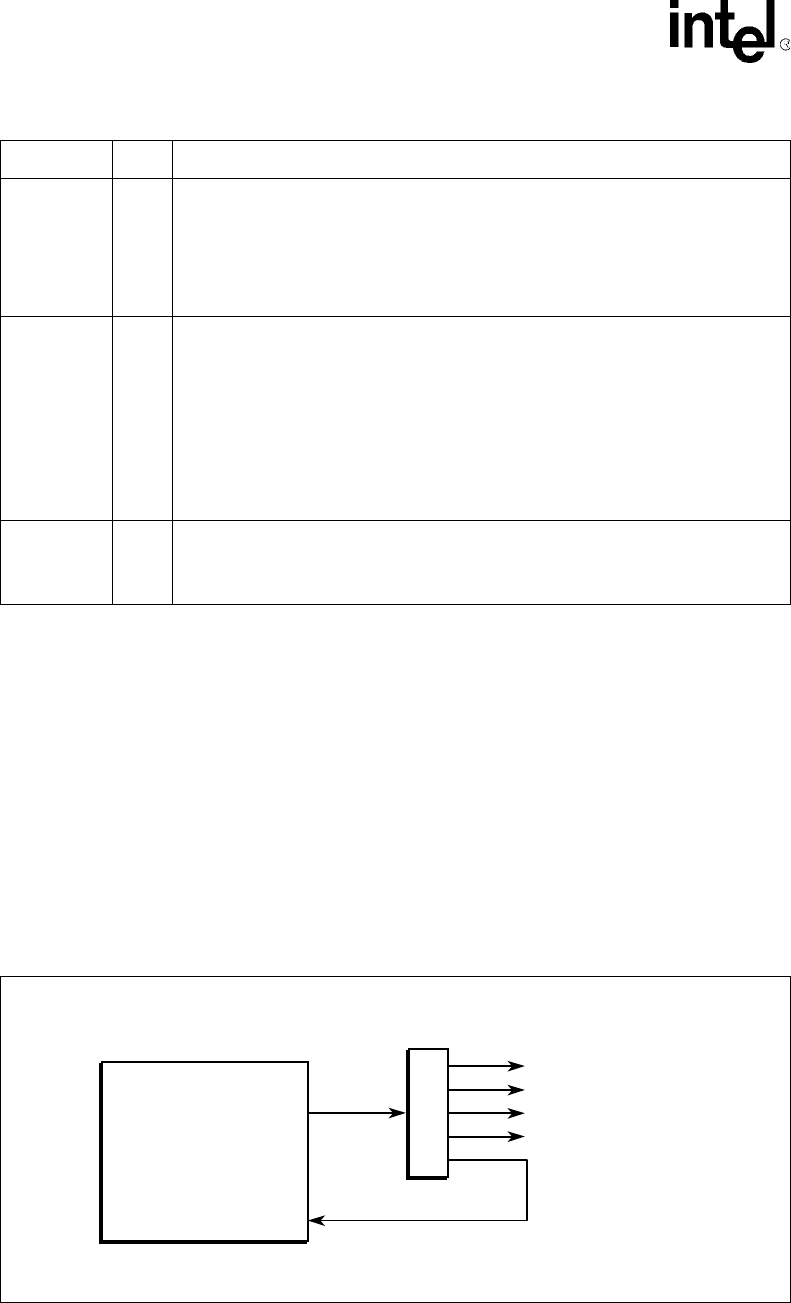

When the secondary clock is not supplied independently, the secondary clock output implemented on the 21555 can

be used in either synchronous or asynchronous mode. The 21555 secondary clock output, s_clk_o, may be buffered

externally for use with secondary bus devices and the 21555 secondary interface clock input, as shown in

Figure 13. When s_clk_o is used for secondary bus devices, one of the externally buffered clock outputs must be

used for the 21555 secondary clock input, s_clk. This clock output is a buffered version of p_clk and therefore has

the same clock frequency as p_clk. An exception is when the primary bus is operating at 66 MHz and the secondary

bus operates at 33 MHz, then the 21555 divides s_clk_o by 2 to generate a 33 Mhz clock (See Section 7.3).

Signal s_clk_o is disabled and driven low when the 21555 samples pr_ad[5] low during reset. Signal s_clk_o may

also be disabled by setting the s_clk_o Disable bit in the Chip Control 0 configuration register.

.

s_clk I

Secondary interface PCI CLK. This signal provides timing for all transactions on the

secondary PCI bus. All secondary PCI inputs are sampled on the rising edge of s_clk,

and all secondary PCI outputs are driven from the rising edge of s_clk. The 21555

operates in a frequency range from 0 MHz to 66 MHz in synchronous mode. In

asynchronous mode the 21555 supports a clocking ratio (defined p_clk : s_clk or

s_clk : p_clk) of a maximum ratio 2.5 : 1 with the upper frequency limit for either clock

input being 66MHz

s_clk_o O

Secondary interface PCI CLK output.

Signal s_clk_o is a buffered version of p_clk. The 21555 divides p_clk by two to

generate s_clk_o when p_m66ena is asserted high and s_m66ena is asserted low

(the primary is operating at 66 MHz and the secondary is operating at 33 MHz).

This signal is generated from the primary interface clock input, p_clk. This clock

operates at the same frequency of p_clk and may be externally buffered to create

secondary bus device clock signals. When buffered clocks are used, one of the clock

outputs must be fed back to the secondary clock input, s_clk. This clock output can

be disabled by writing the secondary clock disable bit in configuration space, or by

pulling pr_ad[5] low during reset.

s_m66ena I/OD

Secondary interface at 66 MHz. Signal s_m66ena asserted high indicates that the

secondary interface is operating at 66 MHz. The 21555 pulls this signal down when

the primary interface is operating at 33 MHz (p_m66ena low) and the secondary

clock output s_clk_o is enabled.

Figure 13. Synchronous Secondary Clock Generation

Table 20. Primary and Secondary PCI Bus Clock Signals (Sheet 2 of 2)

Signal Name I/O Description

A7497-01

21555

To Secondary Bus

Device Clock Inputs

Low-Skew Clock Buffer

s_clk_o

s_clk