21555 Non-Transparent PCI-to-PCI Bridge User Manual 17

Introduction

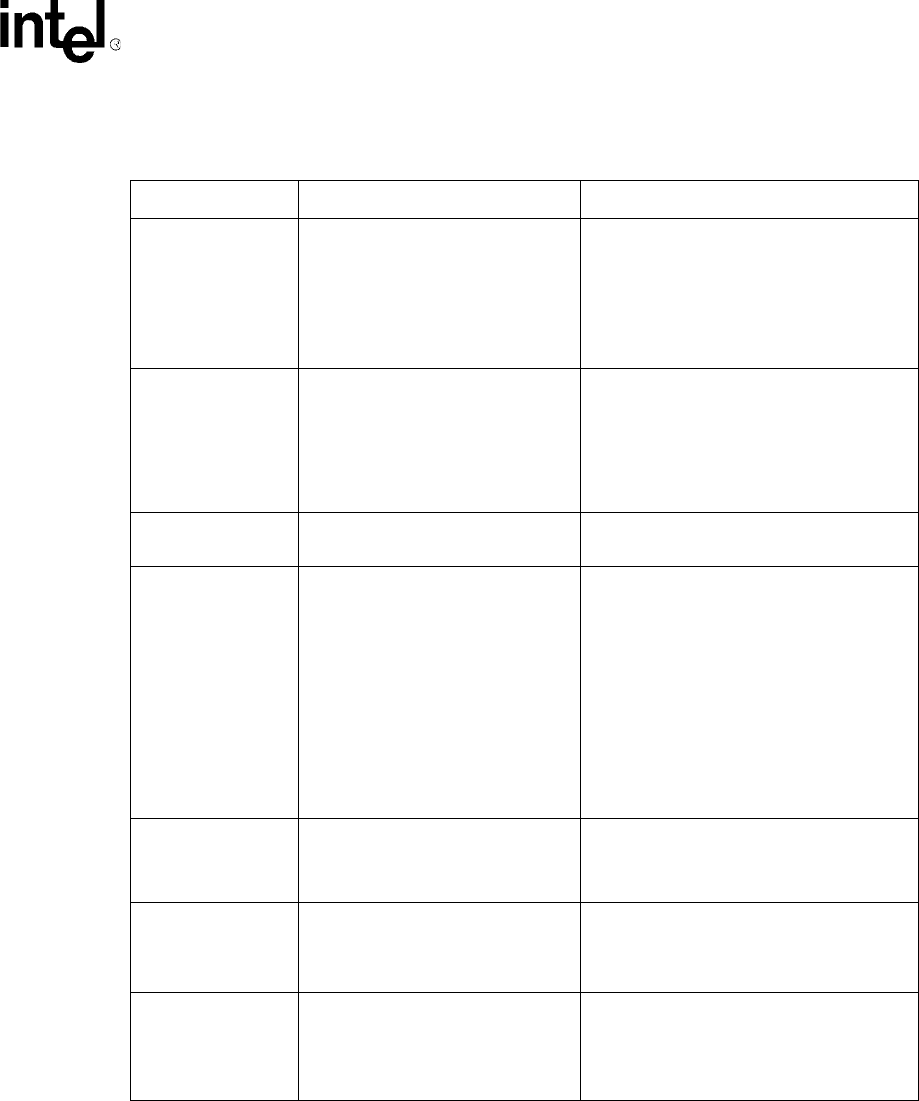

Table 3 shows compares a 21555 and to a transparent PPB.

Table 3. 21555 and PPB Feature Comparison

Feature Non-Transparent PPB or 21555 Transparent PPB

Transaction

forwarding

• Adheres to PPB ordering rules.

• Uses posted writes and delayed

transactions.

• Adheres to PPB transaction error

and parity error guidelines,

although some errors may be

reported differently.

• Adheres to PPB ordering rules.

• Uses posted writes and delayed

transactions.

• Adheres to PPB transaction error and

parity error guidelines.

Address decoding

• Base address registers (BARs)

are used to define independent

downstream and upstream

forwarding windows.

• Inverse decoding is only used for

upstream transactions above the

4GB boundary.

• PPB base and limit address registers are

used to define downstream forwarding

windows.

• Inverse decoding for upstream

forwarding.

Address

translation

Supported for both memory and I/O

transactions.

None. Flat address model is assumed.

Configuration

• Downstream devices are not

visible to host.

• Does not require hierarchical

configuration code (Type 0

configuration header).

• Does not respond to Type 1

configuration transactions.

• Supports configuration access

from the secondary bus.

• Implements separate set of

configuration registers for the

secondary interface.

• Downstream devices are visible to host.

• Requires hierarchical configuration code

(Type 1 configuration header).

• Forwards and converts Type 1

configuration transactions.

• Does not support configuration access

from the secondary bus. Same set of

configuration registers is used to control

both primary and secondary interfaces.

Run

-time resources

Includes features such as doorbell

interrupts, I20 message unit, and so

on, that must be managed by the

device driver.

Typically has only configuration registers; no

device driver is required.

Clocks

Generates secondary bus clock

output.

Asynchronous secondary clock input

is also supported.

Generates one or more secondary bus clock

outputs.

Secondary bus

central functions

Implements secondary bus arbiter.

This function can be disabled.

Drives secondary bus AD, C/BE#,

and PAR during reset. This function

can be disabled.

Implements secondary bus arbiter.

Drives secondary bus AD, C/BE#, and PAR

during reset.