92 21555 Non-Transparent PCI-to-PCI Bridge User Manual

Serial ROM Interface

9.3 SROM Configuration Data Preload Format

Some fields of the 21555 configuration registers may be preloaded using the SROM interface. The first two bits

read from the SROM after the completion of chip reset indicate whether a register preload should be performed.

When the first two bits read as 10b, an auto-load sequence is initiated. The SROM is sequentially read and the data

is shifted along a scan register chain to load the registers listed in Table 114, “Serial Preload Sequence” on

page 180.

9.4 SROM Operation by CSR Access

The 21555 allows SROM access through CSR control. A SROM operation consists of the following three phases:

1. Command phase of 3 bits

2. Address phase of 9 bits

3. Data phase of 8 or more bits

— Read operations may consist of any number of data bits.

— Write operations always consist of 8 data bits.

For a read type operation, the data is driven from the SROM to the 21555 on signal sr_do. For a write operation,

the data is driven from the 21555 to the SROM on signal sr_di.

To perform a SROM access, the initiator should make sure that both the parallel and SROM Start/Busy bits are

clear in the ROM Control CSR. The SROM byte address and the SROM opcode are then written to the ROM

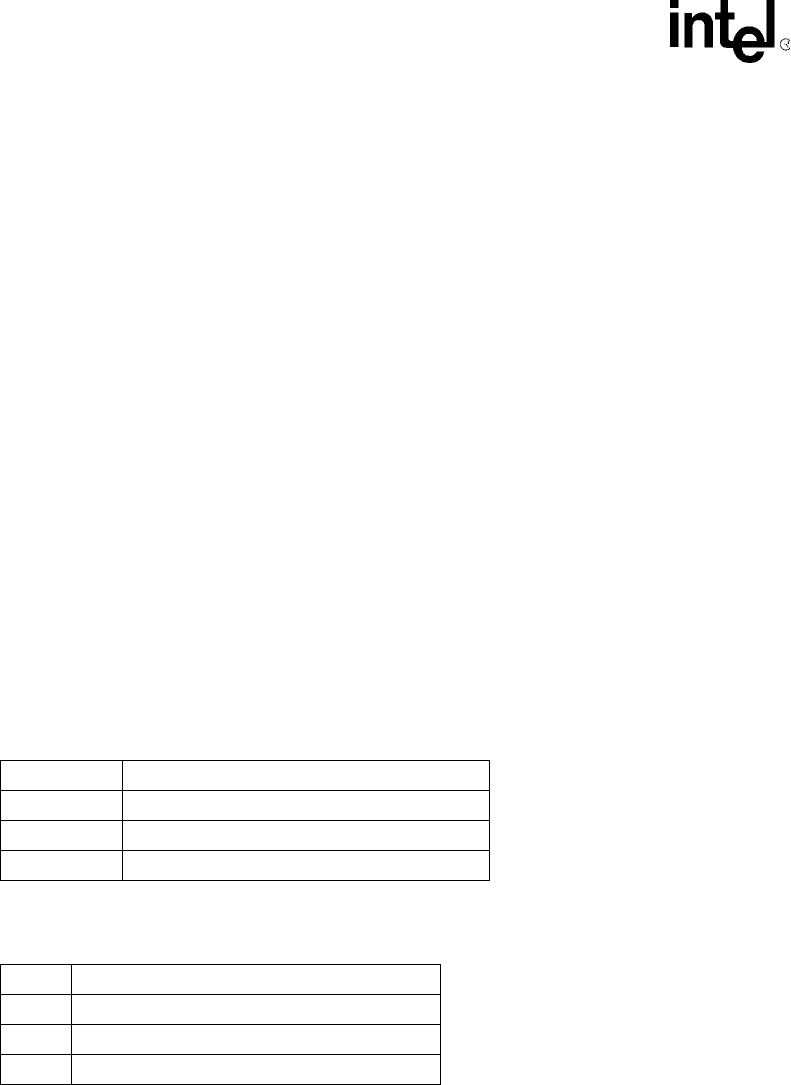

Address CSR. Defined opcodes are:

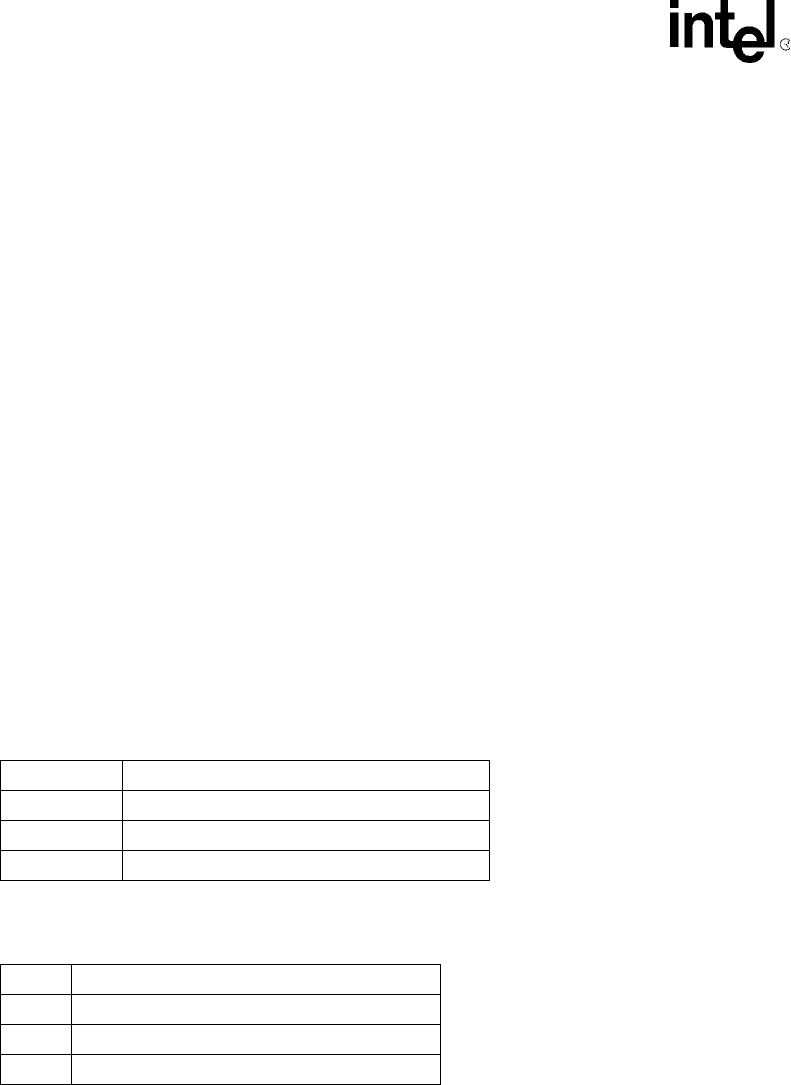

For opcode 00, a byte address is not used and the two most significant address bits [8:7] distinguish between the

four commands:

00 Write enable, write disable, write all, erase all

01 Write

10 Read

11 Erase

00 Write disable

01 Write all

10 Erase all

11 Write enable