21555 Non-Transparent PCI-to-PCI Bridge User Manual 143

List of Registers

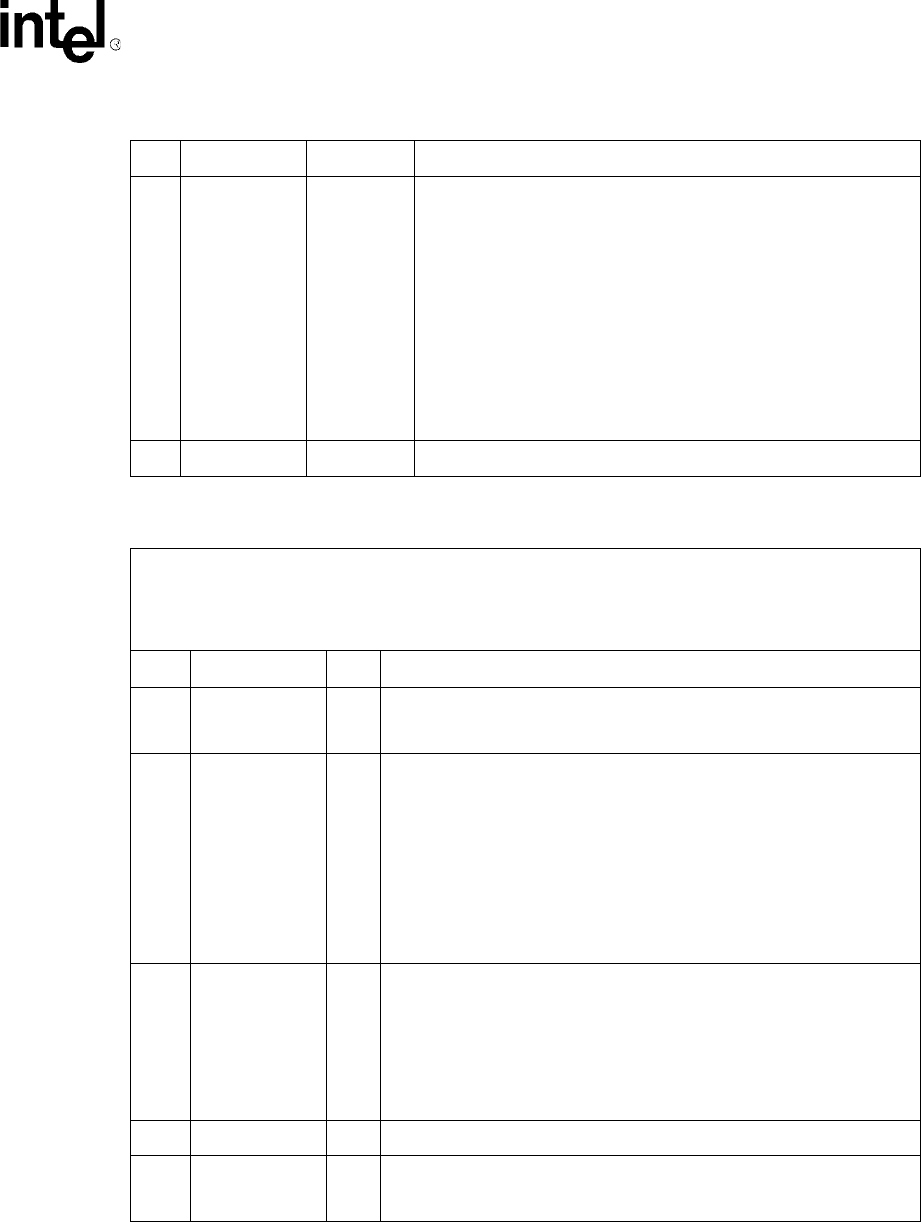

7:1 Reserved R Read only as 0.

8

Upstream

Configuration

Own Bit

R0TS (S)

R(P)

Indicates ownership of the Upstream Configuration Address and

Upstream Configuration Data registers.

• When 0, upstream Configuration Address and Upstream

Configuration Data registers are not owned. When read as a 0

from the secondary interface, this bit is subsequently set to a 1 by

the 21555 if the Upstream Configuration Control bit is a 1.

• When 1, a master owns Upstream Configuration Address and

Upstream Configuration Data registers. When this semaphore

method is used, other masters should not attempt to access

these registers when this bit is a 1. This bit is automatically

cleared once the configuration transaction has completed on the

initiator bus.

• Reset value is 0.

15:9 Reserved R Read only as 0.

Table 49. Configuration CSR (Sheet 1 of 2)

This register is also mapped in memory and I/O space.

• Primary byte offset: 93:92h

• Secondary byte offset: 93:92h

• CSR byte offset: 013:012h

Bit Name R/W Description

0

Downstream

Configuration

Own Status

R

Provides the current value of the Downstream Configuration Own bit. This

bit has no side effects when read.

1

Downstream

Configuration

Control

R/W

Enables the 21555 to perform downstream indirect configuration

transactions.

• When 0, the 21555 will not initiate a configuration transaction on the

secondary interface when the Downstream Configuration Data

register is accessed. The Downstream Configuration Data register is

treated as a reserved register.

• When 1, the 21555 is enabled to perform downstream configuration

transactions when the Downstream Configuration Data register is

accessed.

• Reset value is 0

2

Downstream

Self

-Response

Enable

R/W

Controls the 21555 ability to respond to a configuration transaction that it

generates as a master.

• When 0, the 21555 does not respond to configuration transactions

that it generates.

• When 1, the 21555 does not respond to configuration transactions

that it generates as a master.

• Reset value is 0

7:3 Reserved R Reserved. Returns 0 when read.

8

Upstream

Configuration

Own Status

R

Provides the current value of the Upstream Configuration Own bit. This bit

has no side effects when read.

Table 48. Configuration Own Bits Register