62 21555 Non-Transparent PCI-to-PCI Bridge User Manual

PCI Bus Transactions

• A target retry in response to a posted write is allowed, but only due to temporary conditions,

such as a buffer-full condition.

The ordering rules apply to transactions crossing the bridge in the same direction.

— A posted write.

— A delayed write and read request.

— A delayed write and read completion.

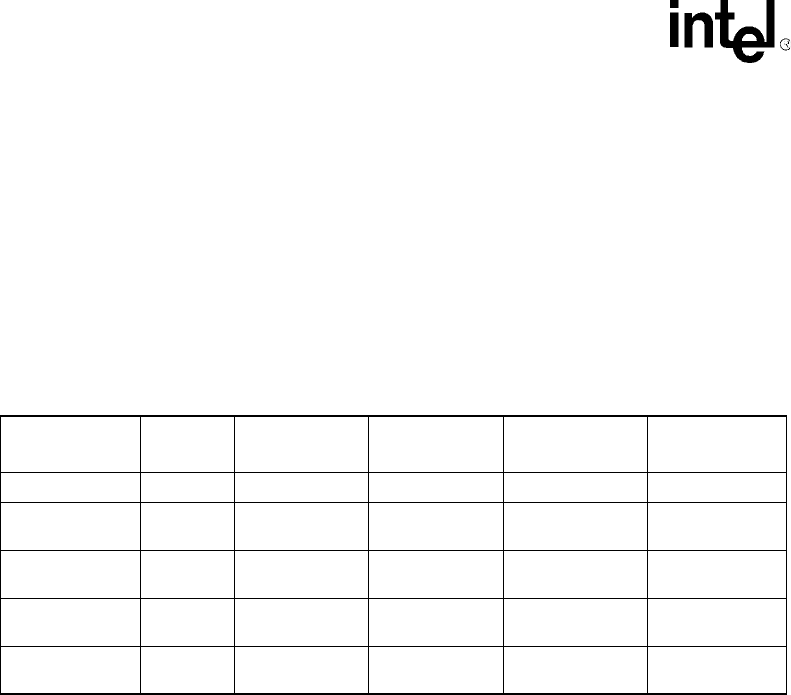

Delayed completions cross the bridge in the opposite direction of its respective delayed request. Table 16 lists the

21555 transaction ordering rules.

The only ordering restriction the 21555 enforces is ordering with respect to posted writes. No other transaction

other than a delayed write completion can pass a posted write. Posted writes are delivered in the order in which they

are accepted.

Delayed transactions may be initiated by the 21555 in any order, and are not necessarily initiated in the order in

which they are received. When the 21555 initiates a delayed transaction, the 21555 can do the following:

• When the Delayed Transaction Order Control configuration bit is not set, the 21555 uses a rotating fairness

algorithm to select which delayed transaction it initiates next, regardless of the type of target termination is

returned (retry, TRDY#, etc.).

• When the Delayed Transaction Order Control configuration bit is set, the 21555 continues to initiate the same

transaction until a response other than target retry is received.

Table 16. 21555 Transaction Ordering Rules

↓ Pass→

Posted

Write

Delayed Read

Request

Delayed Write

Request

Delayed Read

Completion

Delayed Write

Completion

Posted Write No Yes Yes Yes Yes

Delayed Read

Request

No Yes/No

†

Yes/No

†

Yes Yes

Delayed Write

Request

No Yes/No

†

Yes/No

†

Yes Yes

Delayed Read

Completion

No Yes Yes Yes Yes

Delayed Write

Completion

Yes Yes Yes Yes Yes

† Dependent on the state of the Delayed Transaction Ordering bit.