168 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

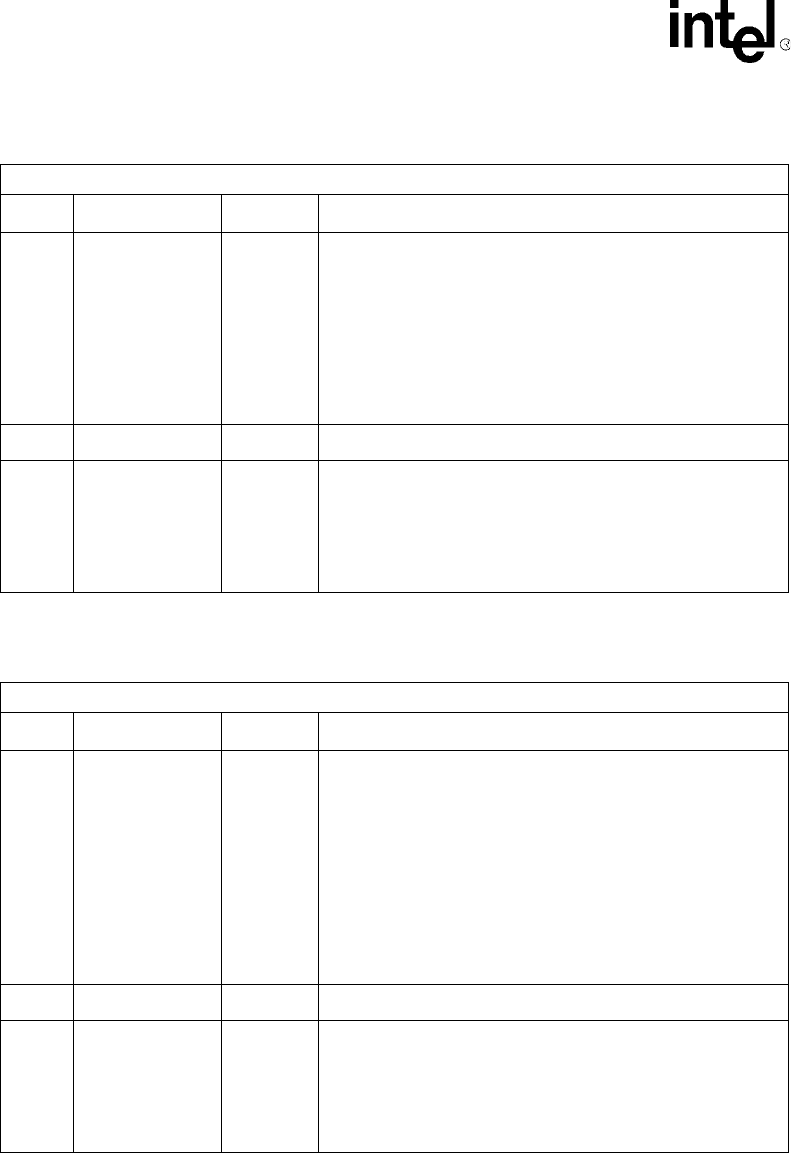

Table 91. I2O Inbound Post_List Counter

Byte Offsets: 05B:058h

Bit Name R/W Description

15:0 Inbound Post Ctr R/(WS)

When read, returns the number of entries in the Inbound

Post_List.

Decrements by 1 when this location is written from the

secondary interface with any data value if bit [31] of this register

is written with a 0 during the same write. When bit [31] is written

with a 1, the 21555 loads the counter with the value written.

Increments when the Inbound Queue at offset 40h is written

from the primary interface.

Reset value : 0

30:16 Reserved R Reserved. Read only as 0.

31 LD_IPC W1TL(S)

Load Inbound Post_List Counter.

• When written with a 1 at the same time as the Inbound Post

Car bits [15:0], it loads the Inbound Post_List Counter with

the value on s_ad[15:0] during that same write.

• When written with a 0, or if s_cbe_l[3] is 1, decrements the

Inbound Post_List Counter. Reads always return 0.

Table 92. I2O Inbound Free_List Counter

Byte Offsets: 05F:05Ch.

Bit Name R/W Description

15:0 Inbound Free Ctr R/(WS)

When read, returns the number of entries in the Inbound

Free_List.

Increments by 1 when this location is written from the secondary

interface with any data value if bit [31] of this register is written

with a 0 during the same write.

When bit [31] is written with a 1, the 21555 loads the counter

with the value written.

Decrements when the Inbound Queue at offset 40h is read from

the primary interface, except when the counter is zero. The

21555 does not decrement when the counter is 0.

Reset value is 0

30:16 Reserved R Reserved. Read only as 0.

31 LD_IFC W1TL(S)

Load Inbound Free_List Counter.

• When written with a 1 at the same time as the Inbound Free

Ctr bits [15:0], loads the Inbound Free_List Counter with the

value on s_ad[15:0] during that same write.

• When written with a 0, or if s_cbe_l[3] is 1, increments the

Inbound Free_List Counter. Reads always return 0.