154 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

Pr

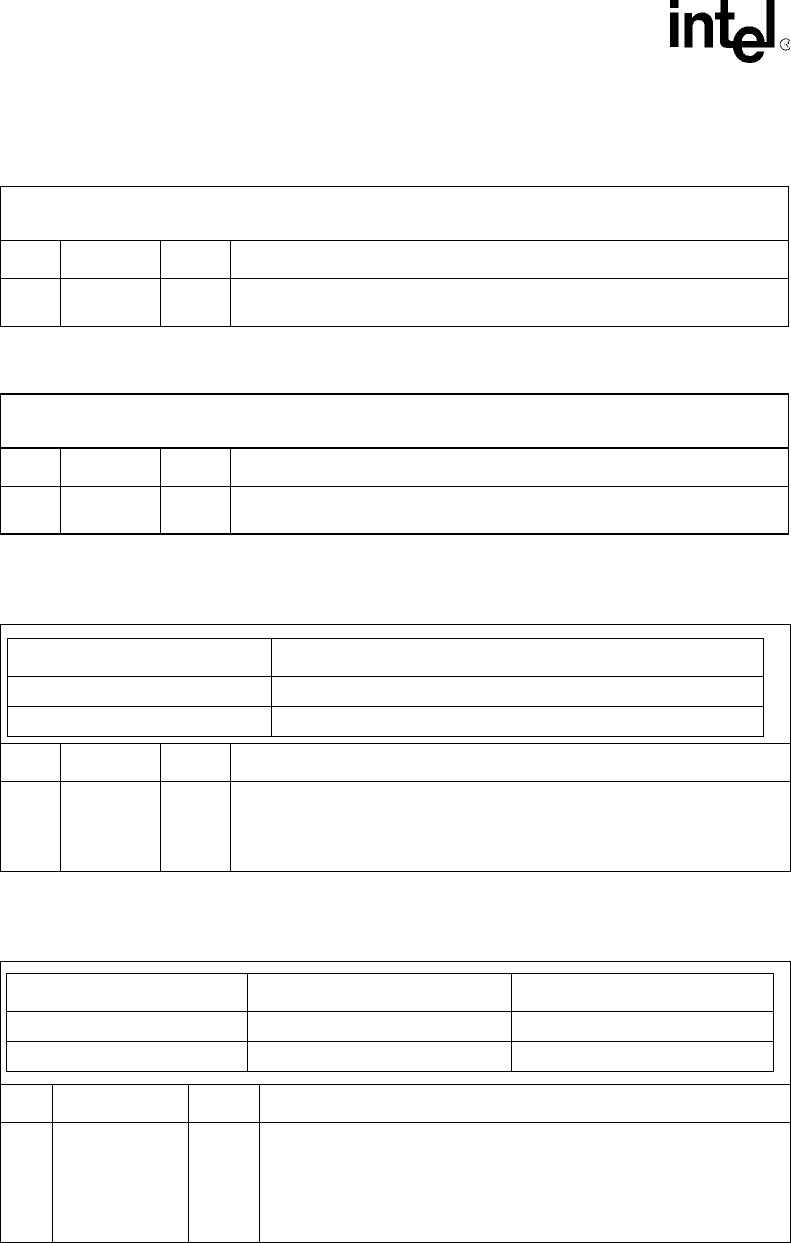

Table 69. Subsystem Vendor ID Register

• Primary byte offset: 2D:2Ch and 6D:6Ch

• Secondary byte offset: 6D:6Ch and 2D:2Ch

Bit Name R/W Description

15:0

Subsystem

Vendor ID

R/(WS)

Identifies the vendor of the add

-in card or subsystem. This register is

initialized by either the local processor or by serial ROM preload.

Table 70. Subsystem ID Register

• Primary byte offset: 2F:2Eh and 6F:6Eh

• Secondary byte offset: 6F:6Eh and 2F:2Eh

Bit Name R/W Description

15:0

Subsystem

ID

R/(WS)

Identifies the vendor

-specific device ID for subsystem. This register is

initialized by either the local processor or by serial ROM preload.

Table 71. Enhanced Capabilities Pointer Register

Bit Name R/W Description

7:0 ECP R

Pointer to the first set of ECP registers. Returns DCh to indicate that the first

set of ECP registers begins at configuration offset DCh. For the 21555, this

points to the Power Management registers.

Reset value is DCh

Table 72. Primary and Secondary Interrupt Line Registers

Bit Name R/W Description

7:0 Interrupt Line R/W

This register is used to communicate interrupt line routing information for

the corresponding interface. This register must be initialized by

initialization code so a default state after reset assertion is not specified.

Initialization code writes this register with a value indicating to which input

of the system interrupt controller the 21555 bus interrupt signal pin INTA#

is connected.

Offsets ECP

Primary byte 34h and 74h

Secondary byte 34h and 74h

Offsets Primary Interrupt Line Secondary Interrupt Line

Primary byte 3Ch 7Ch

Secondary byte 7Ch 3Ch