21555 Non-Transparent PCI-to-PCI Bridge User Manual 91

Serial ROM Interface 9

This chapter presents the theory of operation information about the 21555 Serial ROM (SROM) interface. See

Chapter 16 for specific information about the SROM registers.

The serial ROM interface is used to preload data into the 21555 configuration registers with vendor-specific values.

The format for the serial ROM data is given in Section 9.3. The SROM can be support the Vital Product Data

(VPD) interface as described in Chapter 15.

The SROM interface works with the Microchip 93LC66A* or compatible SROM, which is a byte-organized

Microwire SROM with 4 Kb (512 bytes) of storage. The clock input to the SROM is the primary clock input, p_clk,

operating at a maximum clock frequency of 33 MHz divided by 34. When p_clk is operating above 33 MHz, it is

divided by 68 to generate the SROM clock input. The duty cycle is approximately 50%.

9.1 SROM Interface Signals

The SROM interface consists of four signals, as shown in Table 22. The chip select, sr_cs, has a dedicated pin. The

other signals are multiplexed with the PROM (PROM) interface signals (refer to Table 21). The SROM may be

attached directly to the SROM pins without additional external logic.

9.2 SROMSROM Preload Operation

The SROM interface is used to preload the 21555 configuration registers whenever the 21555 configuration

registers are reset, either through assertion of p_rst_l or s_rst_l, by setting the Chip Reset bit in the Chip Control

Register or after a power management transition from D3

hot

to D0.

Once reset is complete, the 21555 automatically starts a serial read from the ROM by detecting that p_rst_l and

s_rst_l are deasserted and the Chip Reset bit reset to 0 (zero). All of the 21555 initialization data is loaded with a

single read operation by keeping the chip select asserted and toggling the clock. The 21555 returns a target retry to

all configuration accesses until the preload operation is complete. The preload operation takes approximately 550

SROM clock cycles.

When the SROM is not present, the sr_do (pin pr_ad[2]) should be pulled up through an external resistor. When the

SROM is present but register preload is not desired, bits [7:6] of the first byte (the first two bits read) can be any

value except the preload enable sequence 10b. When the 21555 does not detect the preload enable sequence when

reading the first byte, it stops the preload operation. In this case, all configuration registers preloaded with the

SROM remain at their reset value and should be initialized by the local processor before host access.

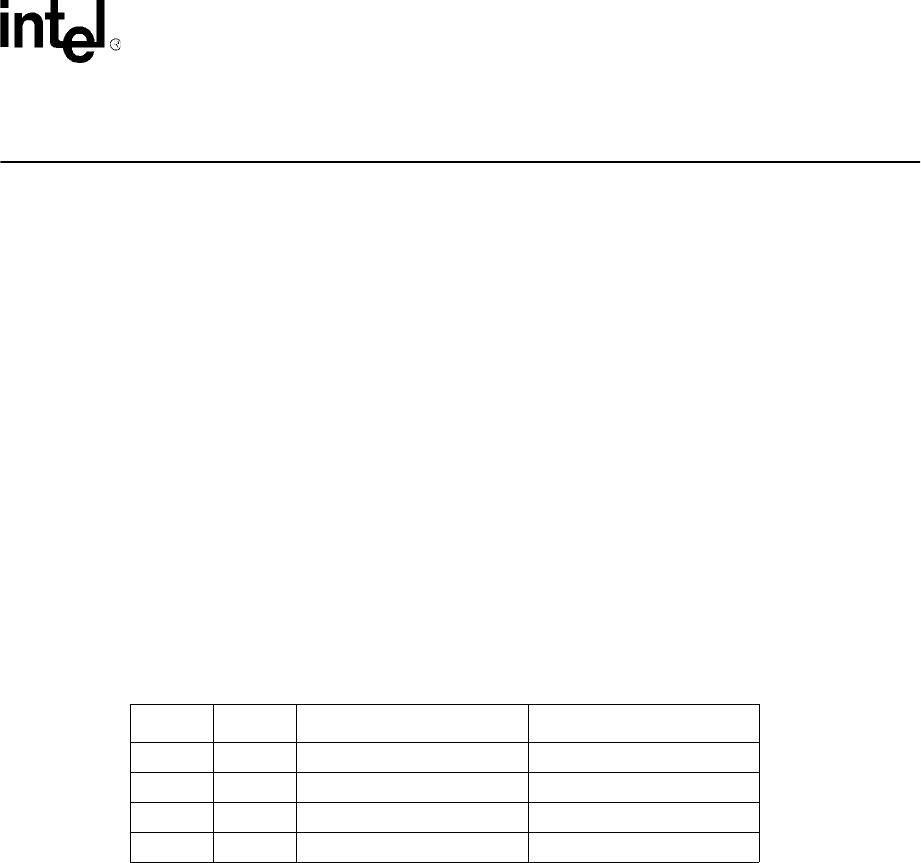

Table 22. SROM Interface Signals

Name Type Description 21555 Pin

sr_cs O Serial ROM Chip Select sr_cs

sr_ck O Serial ROM Clock pr_ad[0]

sr_di O Serial ROM Data In pr_ad[1]

sr_do I Serial ROM Data Out pr_ad[2]