122 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

• “Via Setup” refers to the base address setup register corresponding to that BAR

16.2 Configuration Registers

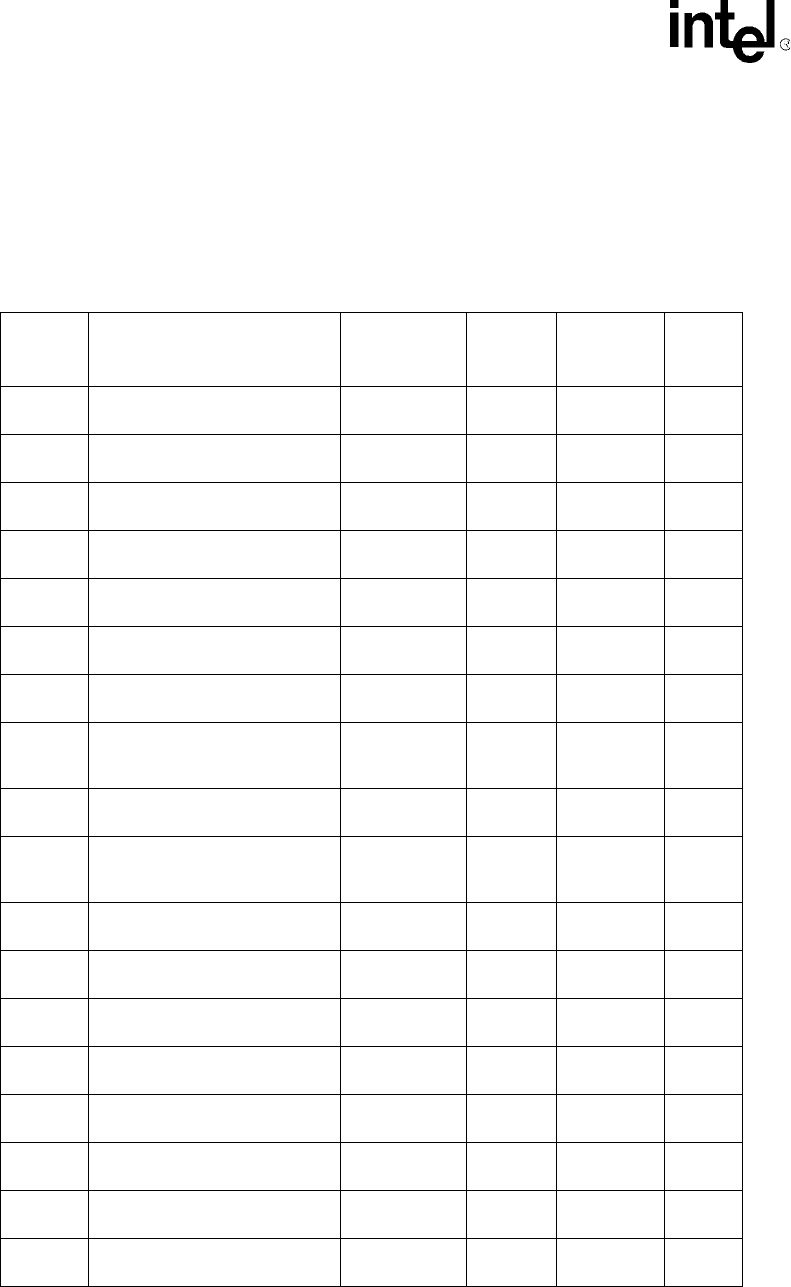

Table 32 lists the configuration space address registers.

Table 32. Configuration Space Address Register (Sheet 1 of 5)

Byte

Offset

(Hex)

Register Name

Reset Value

(Hex)

Preload

Write

Access

Read

Access

01:00

41:40

Vendor ID Register, page 148 1011 — NY

03:02

43:42

Device ID Register, page 148 B555 — NY

05:04 (P)

45:44 (S)

Primary and Secondary

Command Registers, page 149

0000 — YY

07:06 (P)

47:46 (S)

Primary and Secondary Status

Registers, page 150

0290 — YY

08

48

Revision ID (Rev ID) Register,

page 151

Device

dependent

— NY

0B:09 (P)

4B:49 (S)

Primary and Secondary Class

Code Registers, page 152

068000 Y Secondary Y

0C (P)

4C (S)

Primary and Secondary Cache

Line Size Registers, page 152

00 — YY

0D (P)

4D (S)

Primary Latency and Secondary

Master Latency Timer Registers,

page 153

00 — YY

0E

4E

Header Type Register, page 153 00 — NY

0F

4F

BiST Register, page 153 00 Y

[6] Y

[7,3:0]

Secondary

Y

13:10 (P)

53:50 (S)

Primary CSR and Memory 0 BAR 00000000 Via Setup Y Y

17:14 (P)

57:54 (S)

Primary CSR I/O BAR 00000001 — YY

1B:18 (P)

5B:58 (S)

Downstream Memory 1 BAR 000000000 Via Setup Via Setup Y

1F:1C (P)

5F:5C (S)

Downstream Memory 2 BAR 000000000 Via Setup Via Setup Y

23:20 (P)

63:60 (S)

Downstream Memory 3 BAR 00000000 Via Setup Via Setup Y

27:24 (P)

67:64 (S)

Downstream Memory 3 Upper

32 Bits

00000000 Via Setup Via Setup Y

2B:28

6B:67

Reserved 00000000 — NY

2D:2C

6D:6C

Subsystem Vendor ID Register,

page 154D

0000 Y Secondary Y