21555 Non-Transparent PCI-to-PCI Bridge User Manual 145

List of Registers

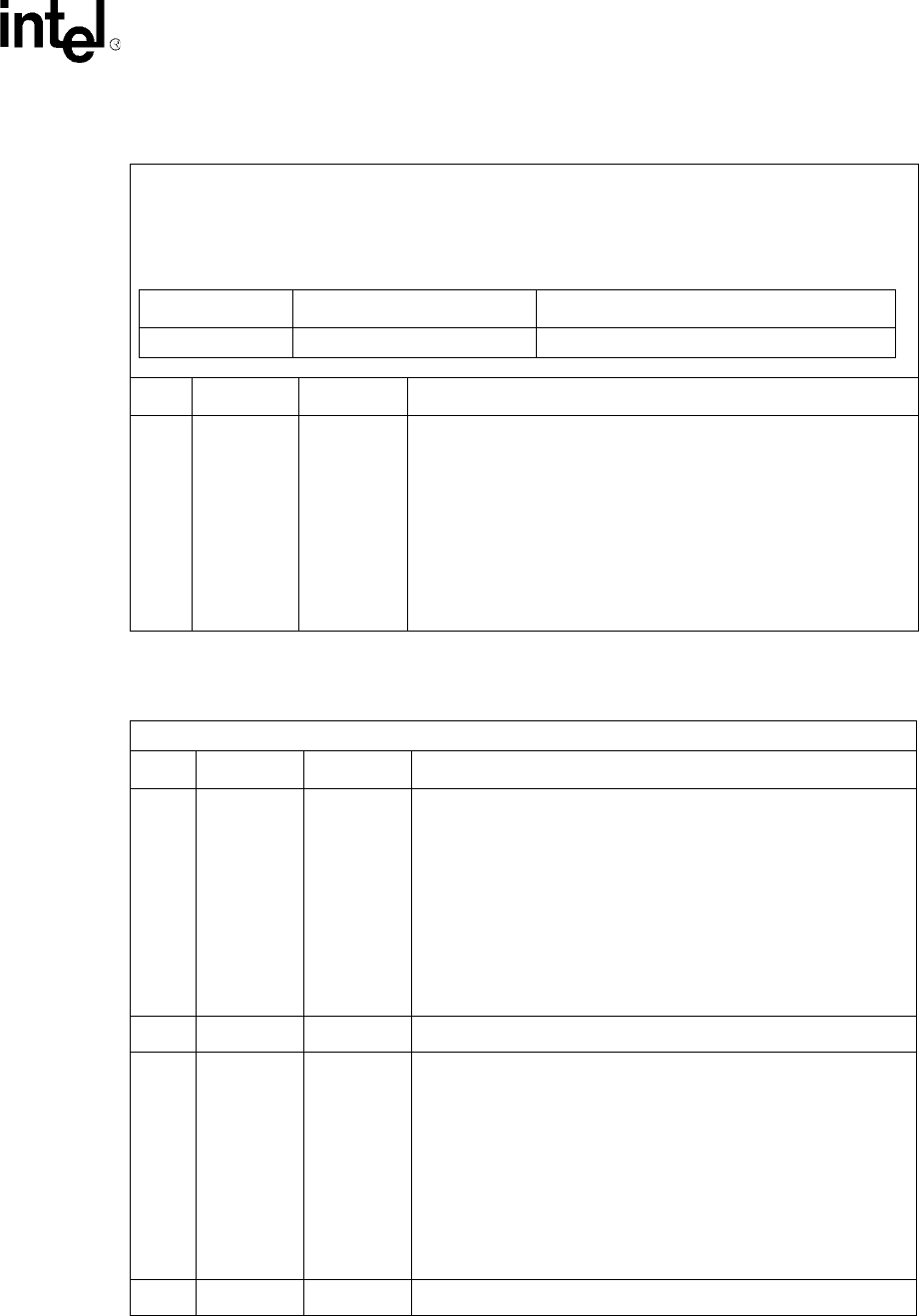

Table 51. Downstream I/O Data and Upstream I/O Data Registers

The Downstream I/O Data register is used for I/O transactions to be initiated on the secondary

bus, and the Upstream I/O Data register is used for I/O transactions to be initiated on the primary

bus. The downstream register can be written from the primary interface only and the upstream

register can be written from the secondary interface only. A downstream transaction is initiated

by a primary interface I/O register access only and an upstream transaction is initiated by a

secondary interface I/O access only.

Bit Name R/W Description

31:0

IO_DATA

(ID)

DID:

R/(WP)

UID:

R/(WS)

Res (Mem)

This register contains the write data driven or the read data returned

from an I/O transaction initiated on the target bus. The Downstream or

Upstream I/O Address register contains the address for this

transaction. The transaction is initiated when this register is written (for

an I/O write) or read (for an I/O read) using an I/O transaction. This

register is treated as a reserved register for all memory accesses. The

byte enables used for this register access are the same byte enables

used for the transaction driven on the target bus. A target retry is

returned to the initiator until the transaction has been completed on

the target bus.

Reset value is 0

Table 52. I/O Own Bits Registers

• Byte Offset: 025:024h

Bit Name R/W Description

0

Downstream

I/O Own Bit

R0TS (P)

R (S)

Indicates ownership of the Downstream I/O Address and

Downstream I/O Data registers.

• When 0, downstream I/O Address and Downstream I/O Data

registers are not owned. When read as a 0 from the primary

interface, this bit is subsequently set to a 1 by the 21555.

• When 1, downstream I/O Address and Downstream I/O Data

registers are owned by a master. When the semaphore method is

used, other masters should not attempt to access these registers

when this bit is a 1. This bit is automatically cleared once the I/O

transaction has completed on the initiator bus.

• Reset value is 0.

7:1 Reserved R Read only as 0.

8

Upstream I/

O Own Bit

R0TS (S)

R (P)

Indicates ownership of the Upstream I/O Address and Upstream I/O

Data registers.

• When 0, upstream I/O Address and Upstream I/O Data registers

are not owned. When read as a 0 from the secondary interface,

this bit is subsequently set to a 1 by the 21555.

• When 1, upstream I/O Address and Upstream I/O Data registers

are owned by a master. When the semaphore method is used,

other masters should not attempt to access these registers when

this bit is a 1. This bit is automatically cleared once the I/O

transaction has completed on the initiator bus.

• Reset value is 0.

15:9 Reserved R Read only as 0.

Offsets Downstream I/O Data Upstream I/O Data

Byte 01B:018h 023:020h