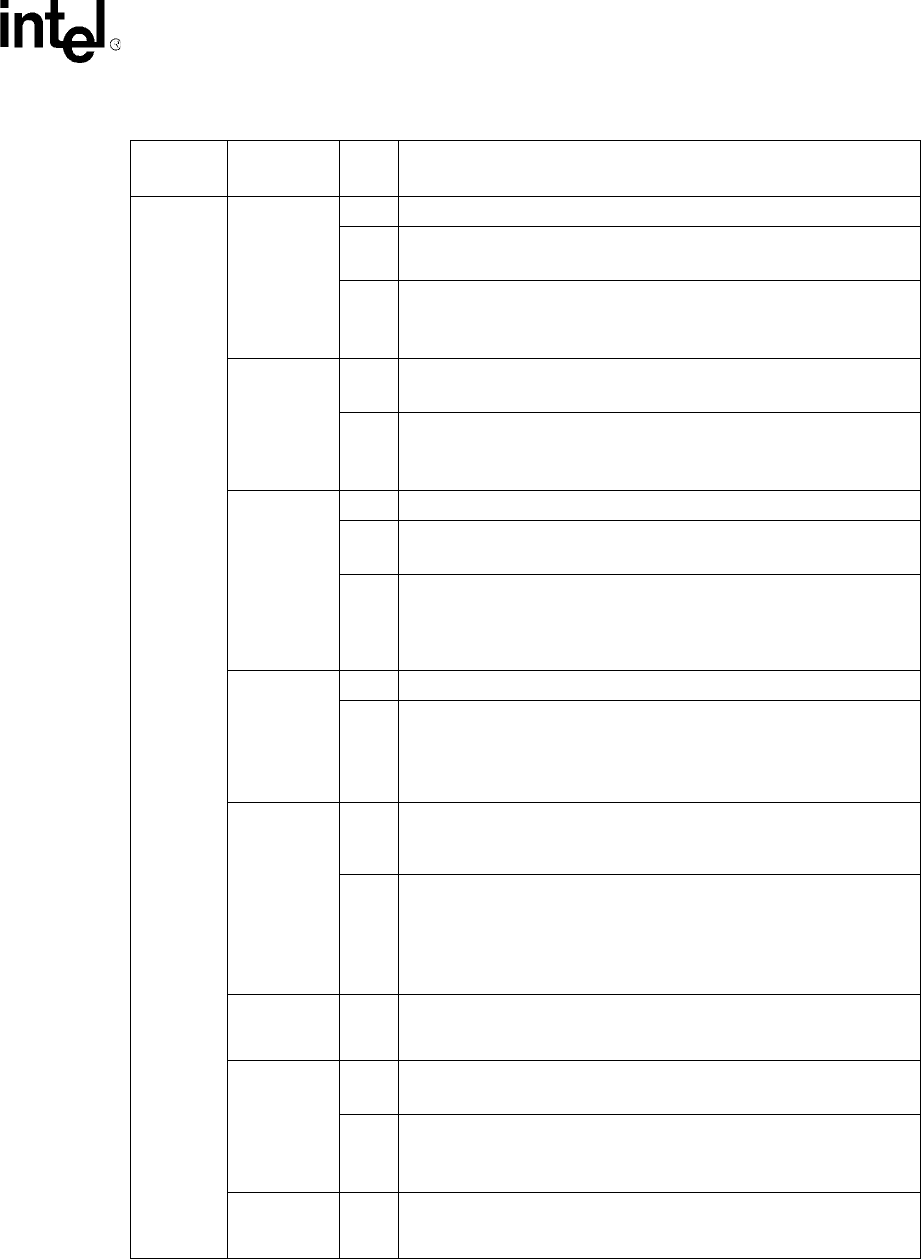

21555 Non-Transparent PCI-to-PCI Bridge User Manual 109

Error Handling

Data Parity

Error on

Secondary

Bus

Downstream

Posted Write

— | 0 Transaction completes normally on secondary bus.

— | 1

• Transaction completes on secondary bus.

• Sets secondary Data Parity Detected bit when s_perr_l is asserted.

1 | 1

• Transaction completes on secondary bus.

• Sets secondary Data Parity Detected bit when s_perr_l is asserted.

• Asserts p_serr_l when no parity error detected on primary bus.

Upstream

Posted Write

— | 0

• Forwards transaction with parity error.

• Sets secondary Detected Parity Error bit.

— | 1

• Forwards transaction with parity error.

• Sets secondary Detected Parity Error bit.

• Asserts s_perr_l.

Downstream

Delayed

Write

— | 0 Transaction completes normally on secondary bus.

— | 1

• Transaction completes normally on secondary bus.

• Sets secondary Data Parity Detected bit when s_perr_l is asserted.

1 | 1

• Transaction completes normally on secondary bus.

• Sets secondary Data Parity Detected bit when s_perr_l is asserted.

• Asserts p_perr_l when returning p_trdy_l to initiator on primary

bus (for both CSR and BAR forwarding mechanisms).

Upstream

Delayed

Write

— | 0 Transaction completes normally on secondary bus.

— | 1

• Returns TRDY# (and STOP# if multiple data phases requested).

• Transaction not forwarded.

• Sets secondary Parity Error Detected bit.

• Asserts s_perr_l.

Downstream

Delayed

Read

— | 0

• Returns read data with bad parity to initiator (for both CSR and BAR

forwarding mechanisms).

• Sets secondary Parity Error Detected bit.

— | 1

• Returns read data with bad parity to initiator (for both CSR and BAR

forwarding mechanisms).

• Sets secondary Parity Error Detected bit.

• Sets secondary Data Parity Detected bit.

• Asserts s_perr_l.

Upstream

Delayed

Read

— |

—

The 21555 is returning data, all action is taken by initiator.

Configuration

Register or

CSR Write

— | 0

• Writes the data normally.

• Sets the secondary Parity Error Detected bit.

— | 1

• Writes the data normally.

• Sets the secondary Parity Error Detected bit.

• Asserts s_perr_l.

Configuration

Register or

CSR Read

— |

—

Returns read data normally.

Table 29. Parity Error Responses (Sheet 3 of 3)

Type of

Error

Type of

Transaction

PER

†

P|S

Action Taken

† PER: Parity Error Response bit (Primary | Secondary).