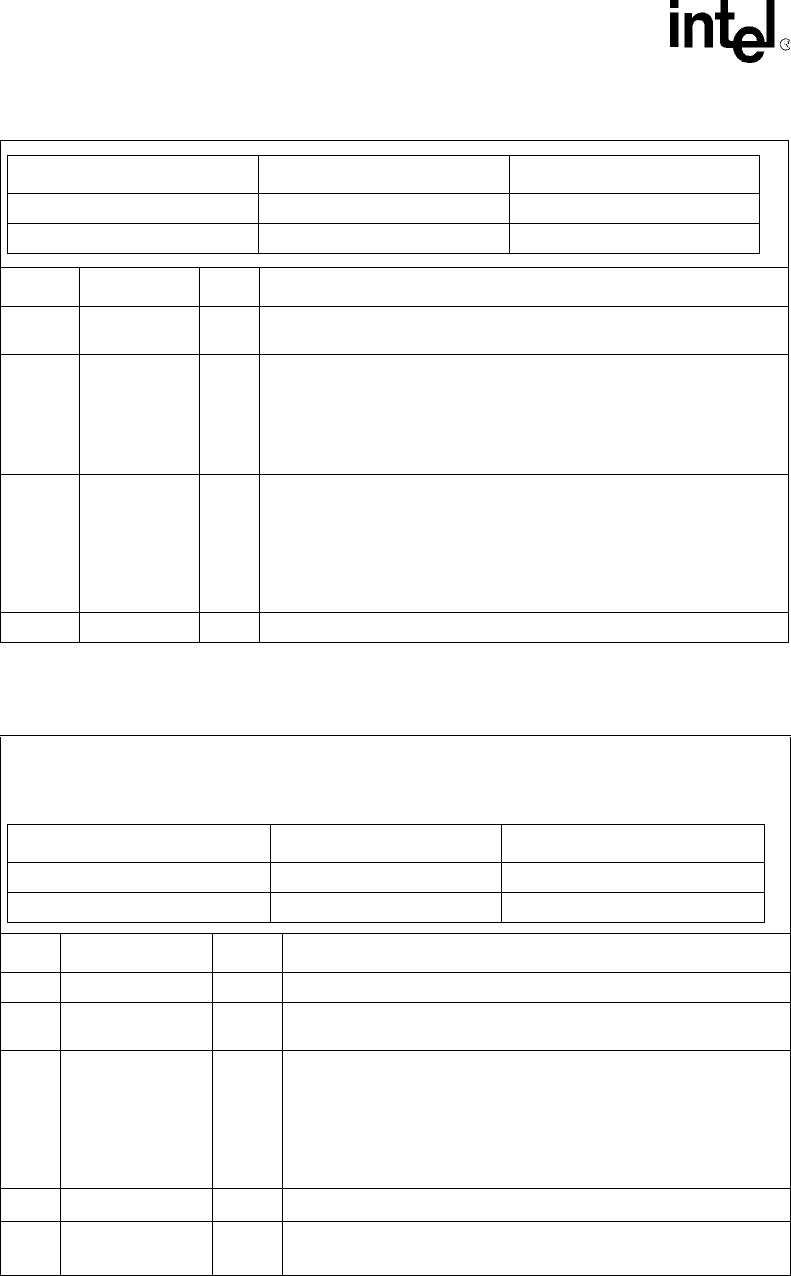

150 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

7

Wait Cycle

Control

R

Reads as zero to indicate the 21555 does not perform address or data

stepping.

8

SERR#

Enable

R/W

Controls the enable for SERR# on the corresponding interface.

• When 0, SERR# cannot be driven by the 21555.

• When 1, SERR# may be driven low by the 21555 under the

conditions described in Chapter 12.

• Reset value is 0.

9

Fast

Back

-to-Back

Enable

R/W

Controls the ability of the 21555 to generate fast back

-to-back

transactions on the corresponding bus.

• When 0, the 21555 does not generate back

-to-back transactions.

• When 1, the 21555 is enabled to generate back

-to-back

transactions.

• Reset value is 0.

15:10 Reserved R Reserved. Returns 0 when read.

Table 62. Primary and Secondary Status Registers (Sheet 1 of 2)

Bit Name R/W Description

3:0 Reserved R Reserved. Returns 0 when read.

4 ECP Support R

Enhanced Capabilities Support Indicator. Reads as 1 to indicate that

the Enhanced Capabilities Port is supported.

5 66 MHz Capable R

66 MHz Capable Indication.

Reads as 0 to indicate that the corresponding interface operates at a

maximum frequency of 33 MHz.

Reads as 1 to indicate that the corresponding interface is 66 MHz

capable.

Product derivatives hardcode this to either 0 or 1.

6 Reserved R Reserved. Returns 0 when read.

7

Fast Back

-to-Back

Capable

R

Reads as 1 to indicate that the 21555 is able to respond to fast

back

-to-back transactions on the corresponding interface.

Table 61. Primary and Secondary Command Registers (Sheet 2 of 2)

Bit Name R/W Description

Offsets Primary Command Secondary Command

Primary byte 05:04h 45:44h

Secondary byte 45:44h 05:04h

The bits described in Table 62 reflect the status of the 21555 primary interface for the Primary Status register,

and of the secondary interface for the Secondary Status register. W1TC indicates that writing a 1 to that bit

clears the bit to 0. Writing a 0 has no effect.

Offsets Primary Status Secondary Status

Primary byte 07:06h 47:46h

Secondary byte 47:46h 07:06h