21555 Non-Transparent PCI-to-PCI Bridge User Manual 87

Parallel ROM Interface

.

8.5 PROM Dword Read

A Dword read is performed on the PROM interface when a read is initiated on the primary bus whose address falls

into the address range defined by the Table 107, “Primary Expansion ROM BAR” on page 175. The 21555 treats a

memory read through the Table 107, “Primary Expansion ROM BAR” on page 175 as a delayed read and returns a

target retry to the initiator. The 21555 performs four consecutive byte reads of the ROM. When the four byte reads

are complete, the 21555 returns the read data to the initiator on the next read attempt to that address to complete the

delayed transaction. The 21555 automatically sets the PROM Start/Busy bit upon initiation of the read and clears

the bit when the ROM read is complete.

Note: The 21555 uses the ROM Address CSR to hold for comparison the address decoded in the Primary

Expansion ROM address space. The CSR access method should not be used for the PROM when

reads to the PROM through the Table 107, “Primary Expansion ROM BAR” on page 175 are

taking place, because the address for the CSR access can become corrupted by a Expansion ROM

BAR read.

The delayed transaction mechanism for the expansion ROM BAR does not support multiple masters. Assume the

21555 completes a ROM Dword read on the ROM interface, but before the data is returned to the master a

transaction using a different offset in the expansion ROM BAR range is initiated. The 21555 discards the current

completed transaction and queues the second transaction. When the first transaction had not been completed on the

ROM interface, a target retry would have been returned.

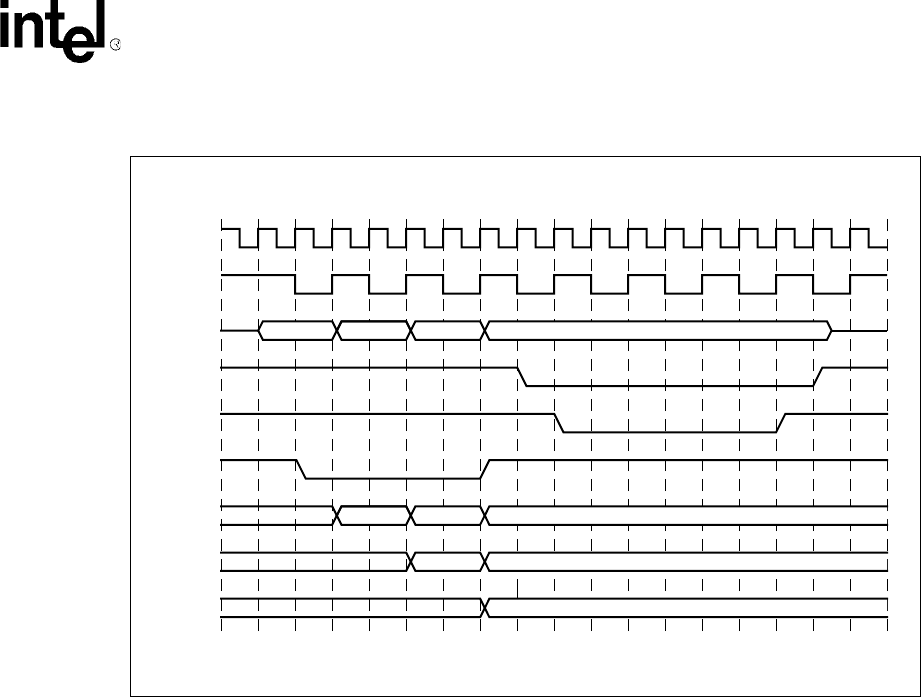

Figure 16. PROM Write Timing

A7471-01

pr_clk

p_clk

pr_ad[7:0]

d[7:0]

pr_cs_l

pr_wr_l

pr_ale_l

a[7:0]

a[15:8]

a[23:16]

A3 A2

Write Data [7:0]

A1

A3 A2 A1 = Address[7:00]

A3 A2 = Address[15:8]

A3 = Address[23:16]