126 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.3 Control and Status Registers

The control and status registers are memory mapped in the Primary CSR and Memory 0 Base Address window and

the Secondary CSR Base Address window. These registers are I/O mapped in the Primary CSR I/O BAse Address

window and the Secondary CSR I/O Base Address window. Offsets are referenced from these base addresses.

Table 33 lists the CSR summary. 017:014

EC CompactPCI Hot-Swap

Capability Identifier and Next

Pointer Register, page 189

Hot-Swap Cap ID

Hot-Swap Next Ptr

06 — Secondary N

ED 00 — NN

EE

CompactPCI Hot-Swap Control

Register, page 189

Hot-Swap Control

00x1000b — YN

FF:F0 Reserved 00000000 — NY

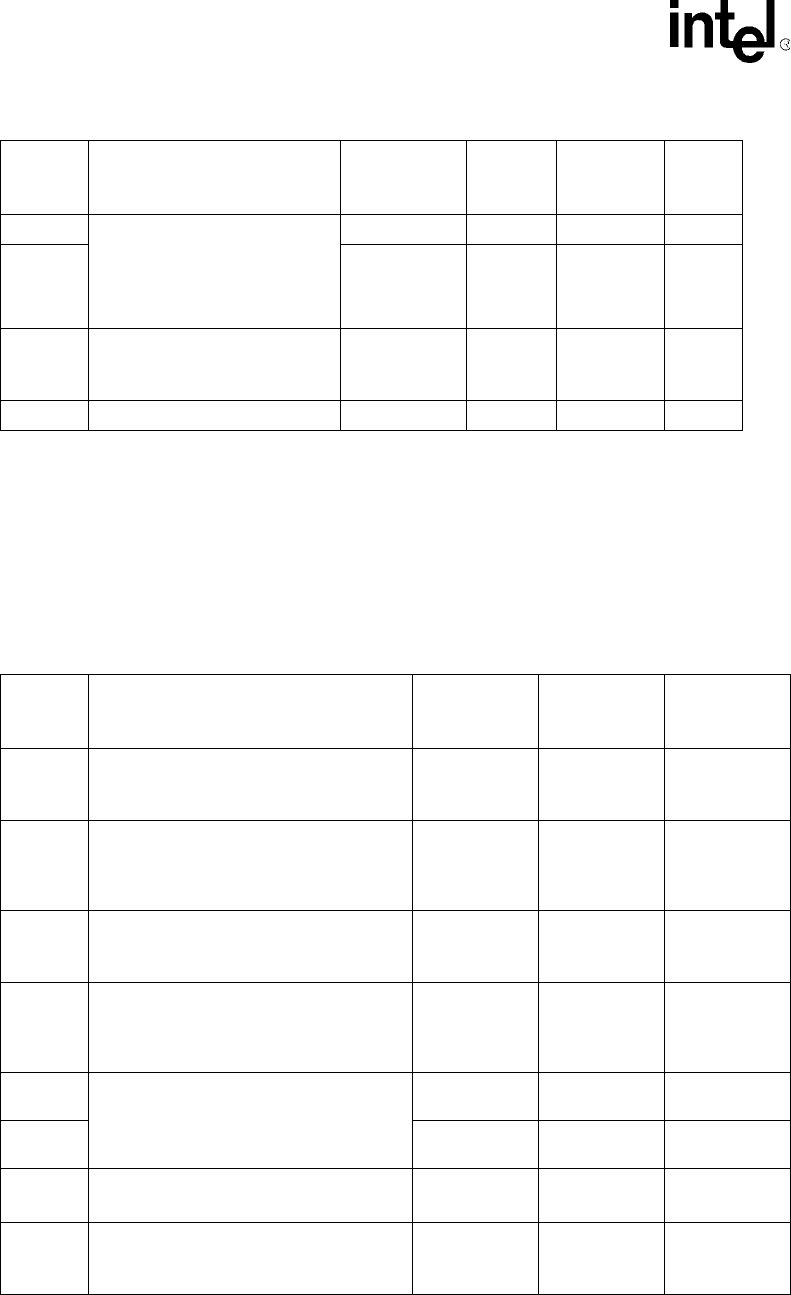

Table 33. CSR Address Map (Sheet 1 of 5)

Byte

Offset

(Hex)

Register Name Reset Value Write Access Read Access

003:000

Downstream and Upstream Configuration

Address Registers, page 141

Downstream Configuration Address

Indeterminate Primary Y

007:004

Downstream Configuration Data and

Upstream Configuration Data Registers,

page 142

Downstream Configuration Data

Indeterminate Primary Primary

00B:008

Downstream and Upstream Configuration

Address Registers, page 141

Upstream Configuration Address

Indeterminate Secondary Y

00F:00C

Downstream Configuration Data and

Upstream Configuration Data Registers,

page 142

Upstream Configuration Data

Indeterminate Secondary Secondary

010 Configuration Own Bits Register, page 142

Configuration Own Byte 0

Configuration Own Byte 1

00 N

Primary Read-

0-to-set

011 00 N

Secondary

Read-0-to-set

013:012

Configuration CSR, page 143

Configuration CSR

0000 Y Y

017:014

Downstream I/O Address and Upstream I/O

Address Registers, page 144

Downstream I/O Address

Indeterminate Primary Y

Table 32. Configuration Space Address Register (Sheet 5 of 5)

Byte

Offset

(Hex)

Register Name

Reset Value

(Hex)

Preload

Write

Access

Read

Access