21555 Non-Transparent PCI-to-PCI Bridge User Manual 153

List of Registers

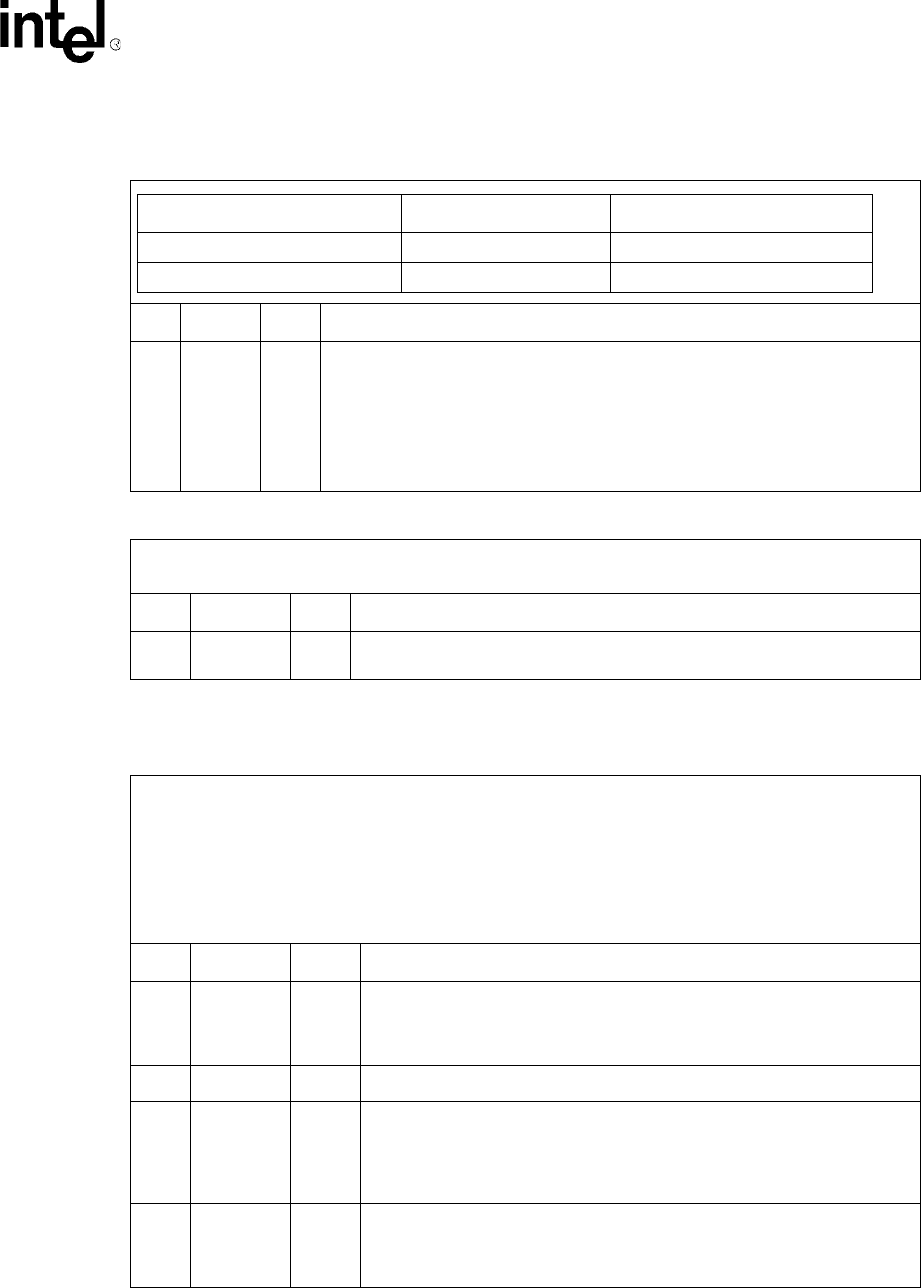

Table 66. Primary Latency and Secondary Master Latency Timer Registers

Bit Name R/W Description

7:0

Master

Latency

Timer

R/W

Master latency timer for the corresponding interface. Indicates the number of PCI

clock cycles from the assertion of FRAME# to the expiration of the timer when the

21555 is acting as a master. All bits are writable, resulting in a granularity of 1 PCI

clock cycle.

• When 0, the 21555 relinquishes the bus after the first data transfer when the

21555’s PCI bus grant has been deasserted.

• Reset value is 00h.

Table 67. Header Type Register

• Primary byte offset: 0Eh and 4Eh

• Secondary byte offset: 0Eh and 4Eh

Bit Name R/W Description

7:0

Header

Type

R

Defines the layout of addresses 00h through 3Fh in configuration space.

Reads as 00h indicating a Type 0 header format.

Table 68. BiST Register

The 21555 does not implement self-test internally and does not directly use the BiST register. However, some

form of self

-test may be desired in the subsystem so mechanisms are provided by the 21555 to support

vendor

-specific usage of the BiST register. The default value of this register is 00h after reset assertion, which

indicates that BiST is not supported. However, after reset the 21555 allows this field to be automatically

preloaded with a value from the serial ROM (when attached) or programmed via the secondary interface by

the local process

• Primary byte offset: 0Fh and 4Fh

• Secondary byte offset: 0Fh and 4Fh

Bit Name R/W Description

3:0

Completion

Code

R/(WS)

The completion code can only be written by the secondary interface (at

secondary offset 0Fh or offset 4Fh). A Completion Code value of 0h indicates

that the device passed its self

-test. Any non-zero value in the Completion

Code indicates that the device failed its self

-test.

5:4 Reserved R Reserved. Read only as 0.

6 Self Test R/W

This bit can be written via the primary interface or secondary interface

configuration registers. Configuration code running on the host processor

sets this bit to 1 to invoke self

-test. The local processor (or some other

device) on the secondary interface clears this bit to 0 to indicate the

completion of the self

-test (after first updating the Completion Code bit field).

7

BiST

Supported

R/(WS)

This bit can be written by the secondary interface (at secondary offset 0Fh or

offset 4Fh) or it may be preloaded using the serial ROM. A value of 1

indicates to configuration software that the device supports self

-test. A value

of 0 indicates that the device does not support self

-test.

Offsets Primary MLT Secondary MLT

Primary byte 0Dh 4Dh

Secondary byte 4Dh 0Dh