21555 Non-Transparent PCI-to-PCI Bridge User Manual 159

List of Registers

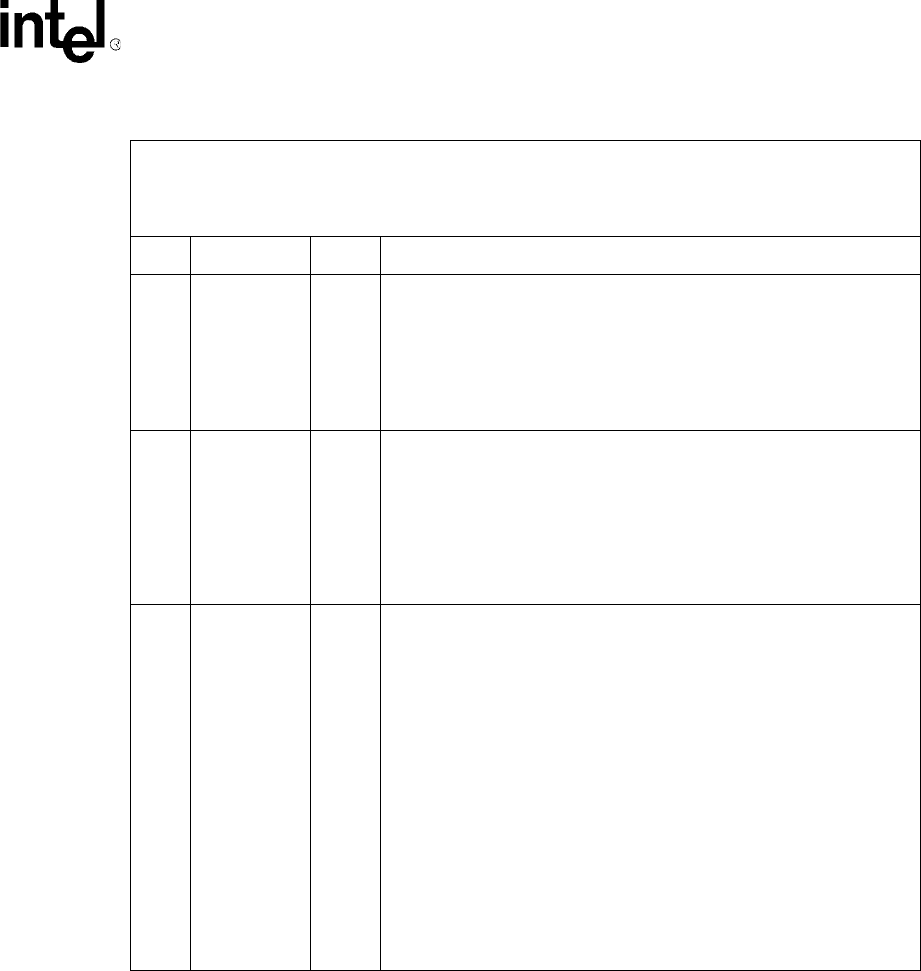

12

LUT Page

Size

Extension Bit

R/W

Allows selection of larger page sizes when programming the page size

field in the Chip Control 1 configuration register.

• When 0, page sizes 256 bytes through 4 MB are available in the page

size field.

• When 1, page sizes 8 MB through 32 MB are available in the page

size field.

• Reset value is 0

13 Retry Counter R/W

Disables or enables all 2

24

retry counters in both directions.

• When 0, all 2

24

retry counters are enabled. When the 21555 attempts

a posted write or delayed transaction as a master and receives 2

24

target retries, the 21555 discards the transaction.

• When 1, all 2

24

retry counters are disabled and do not place any limits

on the number of attempts the 21555 makes when initiating a posted

write or delayed transaction.

• Reset value is 0

15:14 VGA Mode R/W

Enables address decoding and transaction forwarding of the following

VGA transactions:

• Frame buffer memory addresses 000BFFFF:000A0000h

• VGA I/O addresses 3BB:3B0h and 3DF:3C0h, where AD[31:16] =

0000h and AD[15:10] are not decoded.

The following values control how the 21555 decodes and forwards VGA

memory and I/O transactions:

• 00: VGA memory and I/O transactions on the primary and secondary

buses are ignored (unless decoded by some other mechanism).

• 01: VGA memory and I/O transactions on the primary bus are

forwarded to the secondary bus. VGA transactions on the secondary

bus are ignored.

• 10: VGA memory and I/O transactions on the secondary bus are

forwarded to the primary bus. VGA transactions on the primary bus

are ignored.

• 11: Illegal.The 21555 behavior is unpredictable.

Reset value is 00b

Table 77. Chip Control 0 Register (Sheet 4 of 4)

This register may be preloaded by serial ROM or programmed by the local processor before host

configuration.

• Primary byte offset: CD:CCh

• Secondary byte offset: CD:CCh

Bit Name R/W Description