21555 Non-Transparent PCI-to-PCI Bridge User Manual 11

Preface 1

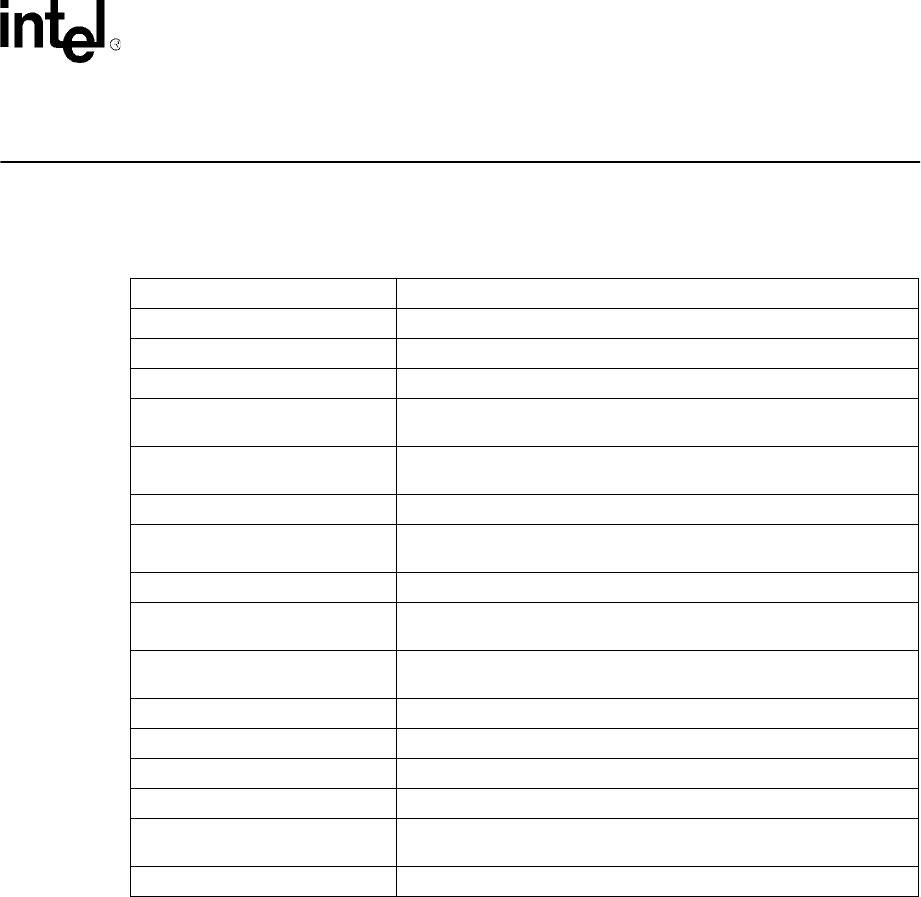

A brief description of the contents of this manual follows.

Chapter 1, “Preface” Provides information about the contents and organization of this book.

Chapter 2, “Introduction” Provides an overview of the 21555 functionality and architecture.

Chapter 3, “Signal Descriptions” Describes PCI signal pins grouped by function.

Chapter 4, “Address Decoding” Contains details about how addresses are decoded.

Chapter 5, “PCI Bus Transactions”

Describes how the 21555 implements

the theory of operation about PCI

transactions.

Chapter 6, “Initialization

Requirements”

Describes the reset operation and initialization requirements.

Chapter 7, “Clocking” Describes 21555 clocking support.

Chapter 8, “Parallel ROM

Interface”

Describes the 21555 Parallel ROM Interface.

Chapter 9, “Serial ROM Interface” Describes the 21555 Serial ROM Interface.

Chapter 10, “Arbitration”

Explains how 21555 implements primary and secondary PCI bus

arbitration.

Chapter 11, “Interrupt and

Scratchpad Registers”

Describes interrupt support and scratchpad registers.

Chapter 12, “Error Handling” Describes parity error responses and system error reporting.

Chapter 13, “JTAG Test Port” Explains the implementation of JTAG test port.

Chapter 14, “I2O Support” Explains how the 21555 implements an I20 messaging unit.

Chapter 15, “VPD Support” Describes Vital Product Data support through SROM interface.

Chapter 16, “List of Registers”

This chapter contains all of the 21555 register information and contains

a register summary.

Appendix A, “Acronyms” Definition of terms used in this book.