21555 Non-Transparent PCI-to-PCI Bridge User Manual 165

List of Registers

16.6 I2O Registers

This section contains a description of the I2O registers. See Chapter 14 for theory of operation information.

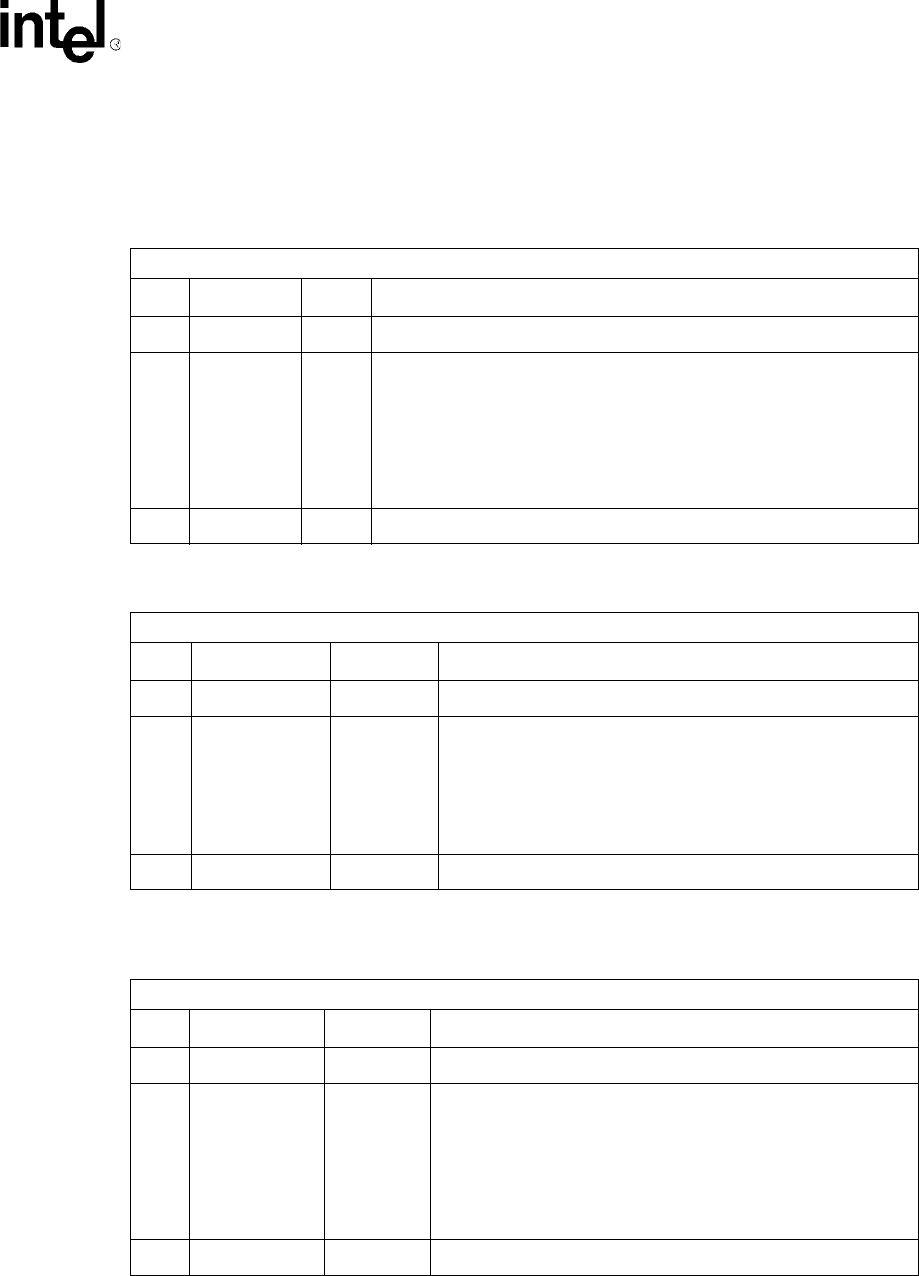

Table 81. I2O Outbound Post_List Status

Byte Offset: 33:30h

Bit Name R/W Description

2:0 Reserved R Reserved. Read only as 0.

3

Outbound

Post Status

R

Reflects the status of the Outbound Post_List.

• When 0, the Outbound Post_List is empty. The 21555 deasserts

p_inta_l (unless it is asserted for other reasons).

• When 1, the Outbound Post_List is not empty. When the Outbound

Post_List Interrupt Mask bit is zero, the 21555 asserts p_inta_l as long

as this status bit is set.

• Reset value is 0

31:4 Reserved R Reserved. Read only as 0.

Table 82. I2O Outbound Post_List Interrupt Mask

Byte Offset: 37:34h

Bit Name R/W Description

2:0 Reserved R Reserved. Read only as 0.

3

Outbound Post

Mask

R/W

Interrupt mask for Outbound Post_List Status.

• When 0, the 21555 asserts p_inta_l when the Outbound

Post_List Status bit is a 1.

• When 1, the 21555 does not assert p_inta_l when the

Outbound Post_List Status bit is a 1.

• Reset value is 1

31:4 Reserved R Reserved. Read only as 0.

Table 83. I2O Inbound Post_List Status

Byte Offset: 3B:38h

Bit Name R/W Description

2:0 Reserved R Reserved. Read only as 0.

3

Inbound Post

Status

R

Reflects the status of the Inbound Post_List.

• When 0, the Inbound Post_List is empty. The 21555 deasserts

s_inta_l (unless it is asserted for other reasons).

• When 1, the Inbound Post_ List is not empty. When the

Inbound Post_List Interrupt Mask bit is zero, the 21555 asserts

s_inta_l as long as this status bit is set.

• Reset value is 0

31:4 Reserved R Reserved. Read only as 0.