184 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

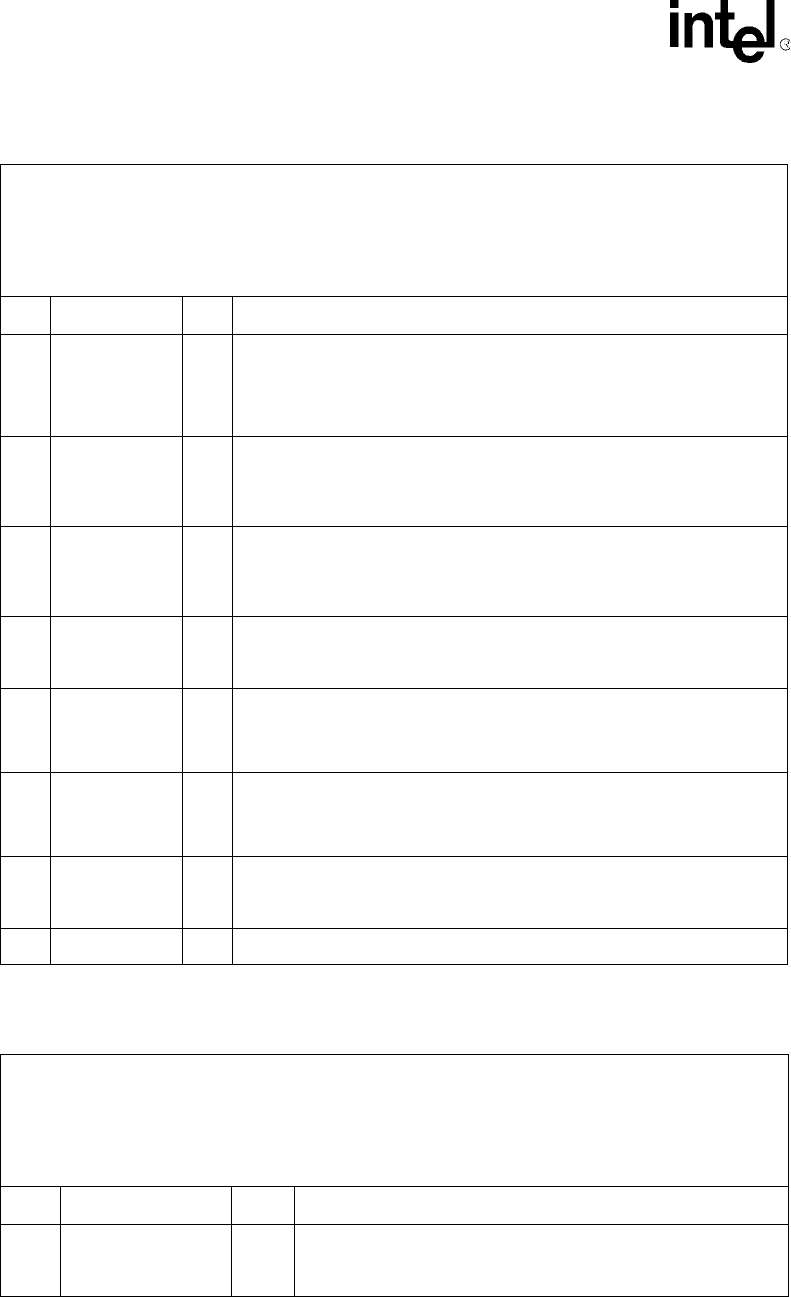

Table 116. Primary SERR# Disable Register

This register may be preloaded by serial ROM or programmed by the local processor before host

configuration. This register controls the ability of the 21555 to assert p_serr_l for a particular condition. When

the bit is a 0, the assertion of p_serr_l is not masked for this event.

When the bit is a 1, the assertion of p_serr_l is masked for this event.

• Primary byte offset: D4h

• Secondary byte offset: D4h

Bit Name R/W Description

0

Downstream

Delayed

Transaction

Master

Time

-out

R/W

Disables p_serr_l assertion when a downstream master time

-out condition

is detected and the downstream transaction is discarded.

Reset value is 0

1

Downstream

Delayed Read

Transaction

Discarded

R/W

Disables p_serr_l assertion when 21555 discards a downstream delayed

read transaction request after receiving 2

24

target retries from secondary bus

target.

Reset value is 0

2

Downstream

Delayed Write

Transaction

Discarded

R/W

Disables p_serr_l assertion when 21555 discards a downstream delayed

write transaction request after receiving 2

24

target retries from secondary

bus target.

Reset value is 0

3

Downstream

Posted Write

Data Discarded

R/W

Disables p_serr_l assertion when 21555 discards a downstream posted

write transaction after receiving 2

24

target retries from secondary bus target.

Reset value is 0

4

Target Abort

during

Downstream

Posted Write

R/W

Disables p_serr_l assertion when 21555 detects a target abort on the

secondary interface in response to a downstream posted write.

Reset value is 0

5

Master Abort

during

Downstream

Posted Write

R/W

Disables p_serr_l assertion when the 21555 detects a master abort on the

secondary interface when initiating a downstream posted write.

Reset value is 0

6

Downstream

Posted Write

Parity Error

R/W

Disables p_serr_l assertion when the 21555 detects s_perr_l asserted

during a downstream posted write.

Reset value is 0

7 Reserved R Reserved. Returns 0 when read.

Table 117. Secondary SERR# Disable Register

This register may be preloaded by serial ROM or programmed by the local processor before host

configuration. This register controls the ability of the 21555 to assert s_serr_l for a particular condition. When

the bit is a 0, the assertion of s_serr_l is not masked for this event.

When the bit is a 1, the assertion of s_serr_l is masked for this event.

• Primary byte offset: D5h

• Secondary byte offset: D5h

Bit Name R/W Description

0

Upstream Delayed

Transaction Master

Timeout

R/W

Disables s_serr_l assertion when an upstream master timeout

condition is detected and the upstream transaction is discarded.

Reset value is 0