58 21555 Non-Transparent PCI-to-PCI Bridge User Manual

PCI Bus Transactions

When using the Quadword boundary, REQ64# asserts every time the transaction is Quadword-aligned (AD[3:0] =

x000b). In some cases, the address is only 2 Dwords away from a cache line boundary, or a 4KB boundary. This

means that if an ACK64# is not received from the target, another transaction may be necessary to get the high

Dword (since FRAME# is only asserted for one cycle, indicating a single data phase).

However, when REQ64# is only asserted when the address is octaword-aligned, instances occur where REQ64#

does not assert, but the address is several Dwords from a disconnect or prefetch boundary. For example, when the

cache line size is 16 Dwords (32 bytes) but the address is Quadword-aligned on Dword address 2 (xxxx xx08h),

there are still 14 Dwords to deliver before the end of a cache line is reached.

Assuming an even distribution of unaligned addresses (which are a minority of all transactions), it is more efficient

to optimize for the 64-bit behavior and assert REQ64# on Quadword-aligned accesses, while losing some

efficiency on those Quadword-aligned transactions near a boundary where ACK64# is not asserted.

When the bandwidth of the initiator interface is twice that of the target interface, then limited flow-through is

allowed. For example, when the initiator is performing a 64-bit transaction, but the corresponding transaction to the

target is a 32-bit transaction. In this case, for cache line sizes of 16 and 32 Dwords, flow-through is allowed only

when a full cache line is accumulated in the read data buffer for memory read multiple transactions, or when half a

cache line is accumulated for memory read line and prefetchable memory read transactions. For cache line sizes of

8 Dwords, flow-through is allowed when 2 Dwords have been accumulated. In limited flow-through only the

standard prefetch boundaries described in Prefetching are used, that is, longer bursts are not accommodated.

However, limited flow-through minimizes the latency when returning read data with a 2:1 bandwidth mismatch.

When the read data queue empties while the 21555 is in limited flow-through mode, the 21555 waits up to seven

cycles and then disconnects if read data is still not available.

When the bandwidth of an initiator interface is four times that of the target (e.g., the initiator is performing a 66

MHz, 64-bit operation), and the target is operating at 33 MHz, 32-bit operation, no flow-through is performed. The

read operation must complete at the target before read data is returned to the initiator. This is to prevent inserting

wait states and possible early disconnects on the initiator bus.

5.4.4.2 Prefetching

The 21555 prefetches read data to the aligned address boundaries listed in Table 15.

The cache line size corresponding to the initiator bus is used for determining prefetch boundaries.

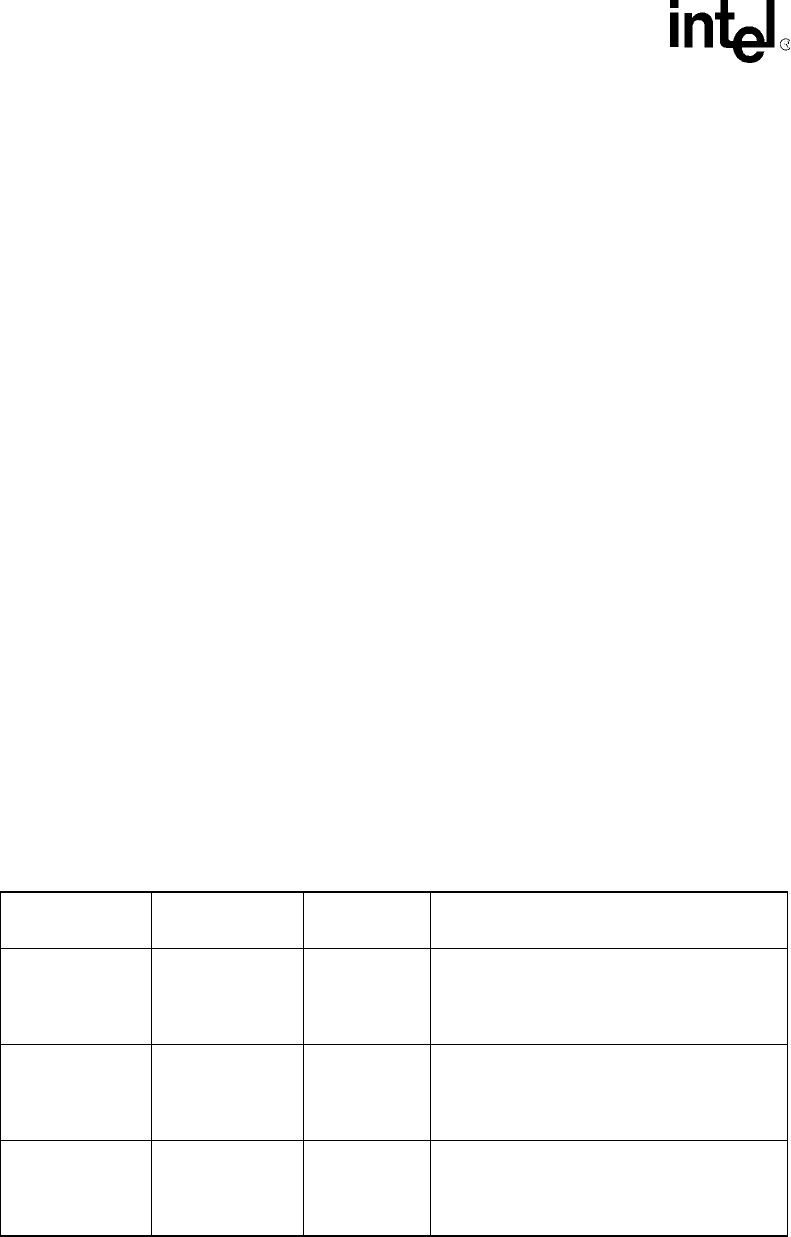

Table 15. Prefetch Boundaries

Read Command

Non

-prefetchable

Range

Prefetchable

Range

In Flow

-Through Mode

Memory Read 1 Dword 1 cache line

Page boundary for transactions in Upstream

Memory 2 range

4KB boundary

Initiator deasserts FRAME#

Memory Read Line 1 cache line 1 cache line

Page boundary for transactions in Upstream

Memory 2 range

4 KB boundary

Initiator deasserts FRAME#

Memory Read

Multiple

2 cache lines 2 cache lines

Page boundary for transactions in Upstream

Memory 2 range

4 KB boundary

Initiator deasserts FRAME#