186 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

.

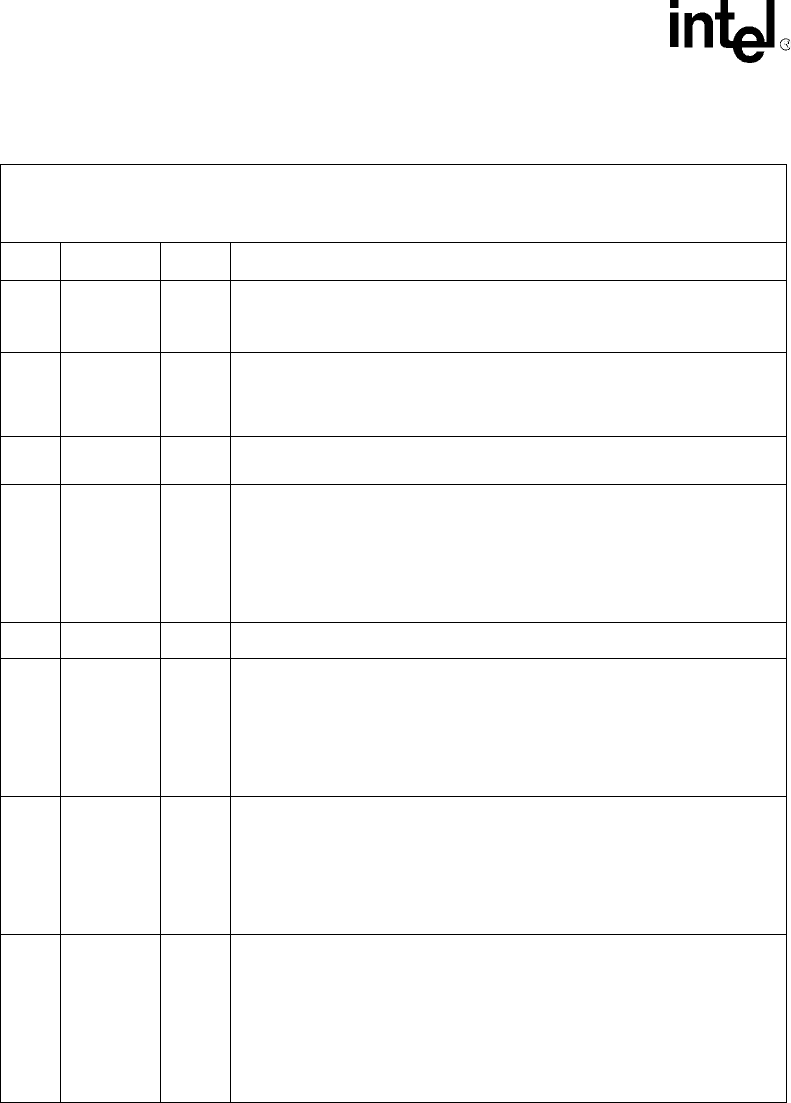

Table 119. Power Management Capabilities Register

Bits [14:9,5,2:0] are loadable through the serial ROM or are programmable by the local processor.

• Primary byte offset: DF:DEh

• Secondary byte offset: DF:DEh

Bit Name R/W Description

2:0 PM Version R/(WS)

Power Management Version. Loadable by serial ROM.

Reset value is Signal 001b to indicate that this device is compliant to the PCI

Power Management Interface Specification, Revision 1.1.

3 PME Clock R

Clock Required for PME# Assertion. Reads as 1 to indicate that a clock is

required to assert PME#, when any of bits [15:11] in this register are

asserted. Read as 0 when bits [15:11] are all 0, indicating that the 21555

does not assert PME#.

4APS R

Auxiliary Power Source. Not defined since the 21555 does not have PME#

support from D3

cold

. Read only as 0.

5DSI R/(WS)

Device

-Specific Initialization. Loadable by serial ROM.

• When 0, indicates that the 21555 does not have device

-specific

initialization requirements.

• When 1, indicates that the 21555 has device

-specific initialization

requirements.

• Reset value is 0

8:6 Reserved R Reserved. Read only as 0.

9 D1 Support R/(WS)

D1 Power State Support Indicator. Loadable by serial ROM.

• When 0, indicates that the 21555 does not support the D1 power

management state.

• When 1, indicates that the 21555 supports the D1 power management

state.

• Reset value is 0

10 D2 Support R/(WS)

D2 Power State Support Indicator. Loadable by serial ROM.

• When 0, indicates that the 21555 does not support the D2 power

management state.

• When 1, indicates that the 21555 supports the D2 power management

state.

• Reset value is 0

15:11

PME

Support

R/(WS)

PME# support. Indicates whether the 21555 asserts p_pme_l when in a

given power state. Bit 11 corresponds to D0; bit 15 corresponds to D3

cold

.

Bits [14:11] are loadable by serial ROM.

Bit 15 always reads as 0 and is not loaded by serial ROM nor writable from

the secondary interface, since the 21555 never asserts PME# when in

D3

cold

.

Reset value is 0 to indicate that the 21555 does not implement the PME#

pin.