21555 Non-Transparent PCI-to-PCI Bridge User Manual 187

List of Registers

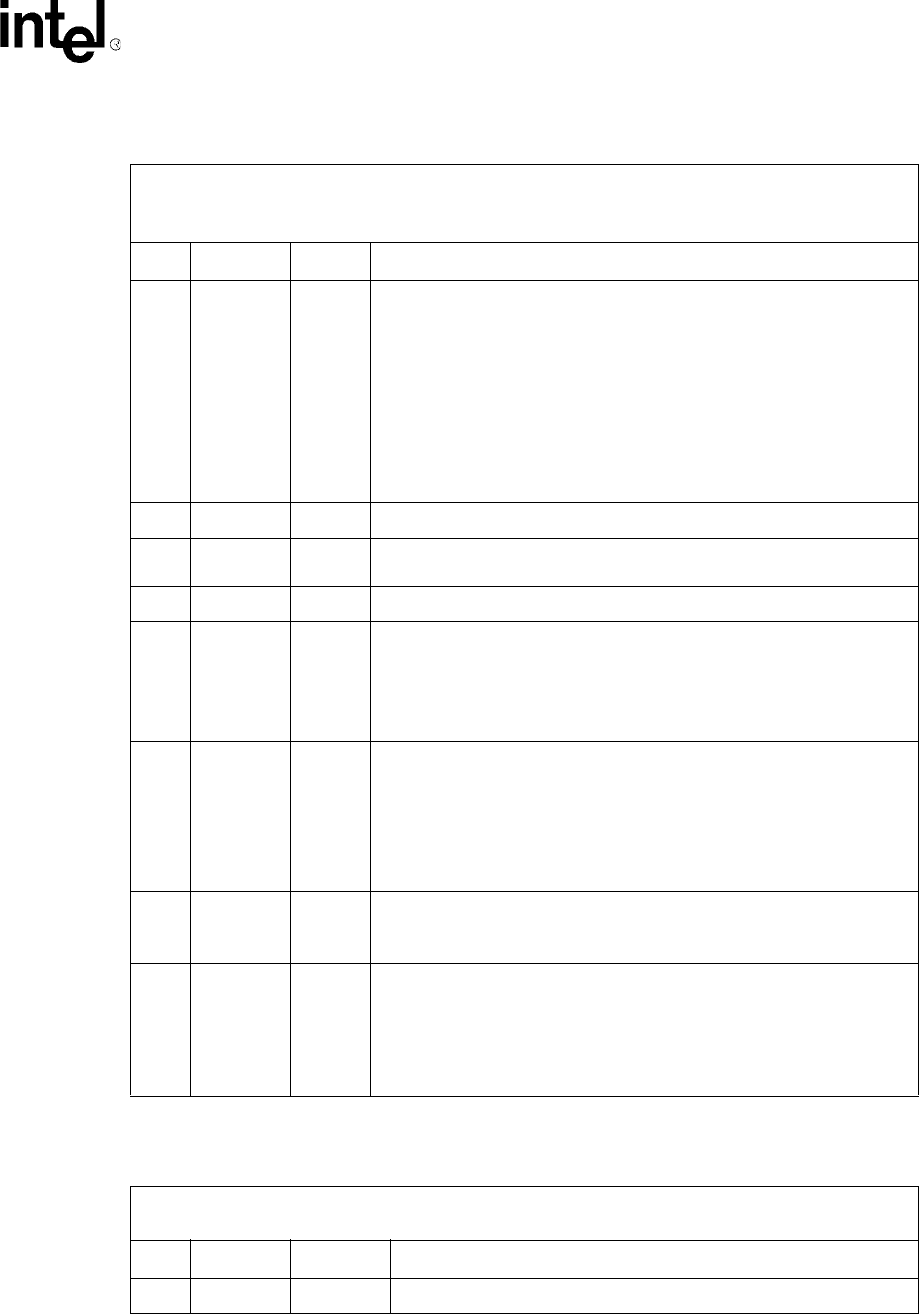

Table 120. Power Management Control and Status Register

Bits [14:13] are loadable by serial ROM or are programmable by the local processor.

• Primary byte offset: E1:E0h

• Secondary byte offset: E1:E0h

Bit Name R/W Description

1:0 PWR State R/W

Power State. Reflects the current power state of the 21555. When an

unimplemented power state is written to this register, the 21555 completes

the write transaction, ignores the write data, and does not change the value

of this field. D0 and D3 are always implemented. Support of D1 and D2 is

determined by serial ROM preload.

00b : D0 (required)

01b : D1 (optional)

10b : D2 (optional)

11b : D3 (required)

Reset value is 00b

3:2 Reserved R Reserved. Read only as 00b.

4DYN DATAR

Dynamic Data. Reads as 0 to indicate that the 21555 does not support

dynamic data reporting.

7:5 Reserved R Reserved. Read only as 000b.

8PME_ENR/W

PME# Enable. Read only as 0 when the PME Support bits are all 0.

Otherwise, this is a read/write bit.

• When 0, the 21555 will not assert p_pme_l.

• When 1, the 21555 is enabled to assert p_pme_l.

• Reset value is 0

12:9 DATA_SEL R/W

Data Select. This register is enabled by loading a “1” for the PM Data

Enable function in the serial ROM. See “Serial Preload Sequence” on

page 16-180. For values of 7:0, this register selects one of eight bytes of

data loaded by serial ROM to be placed in the power management data

register. For values of 15:8, a 0 is returned in the data register.

• When not enabled, this register always returns 0 when read.

• Reset value is 000b.

14:13 Data Scale R/(WS)

Data Scale. Indicates the scaling factor of the value in the power

management data register. Loadable by serial ROM.

Reset value is 00b

15 PME Status R/W1TC

PME Status. The 21555 sets this bit to a 1 when s_pme_l is asserted and

the PME# Support bit for the current power state is a 1. This corresponds to

when the 21555 would normally assert p_pme_l, but regardless of the state

of the PME_En bit.

Writing a 1 clears this bit. Writing a 0 has no effect.

Reset value is 0.

Table 121. PMCSR Bridge Support Extensions

• Primary byte offset: E2h

• Secondary byte offset: E2h

Bit Name R/W Description

7:0 BSE R Bridge Support Extensions. Read only as 00h.