156 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.5.3 Device-Specific Control and Status Registers

This section contains information about the device-specific control and status registers.

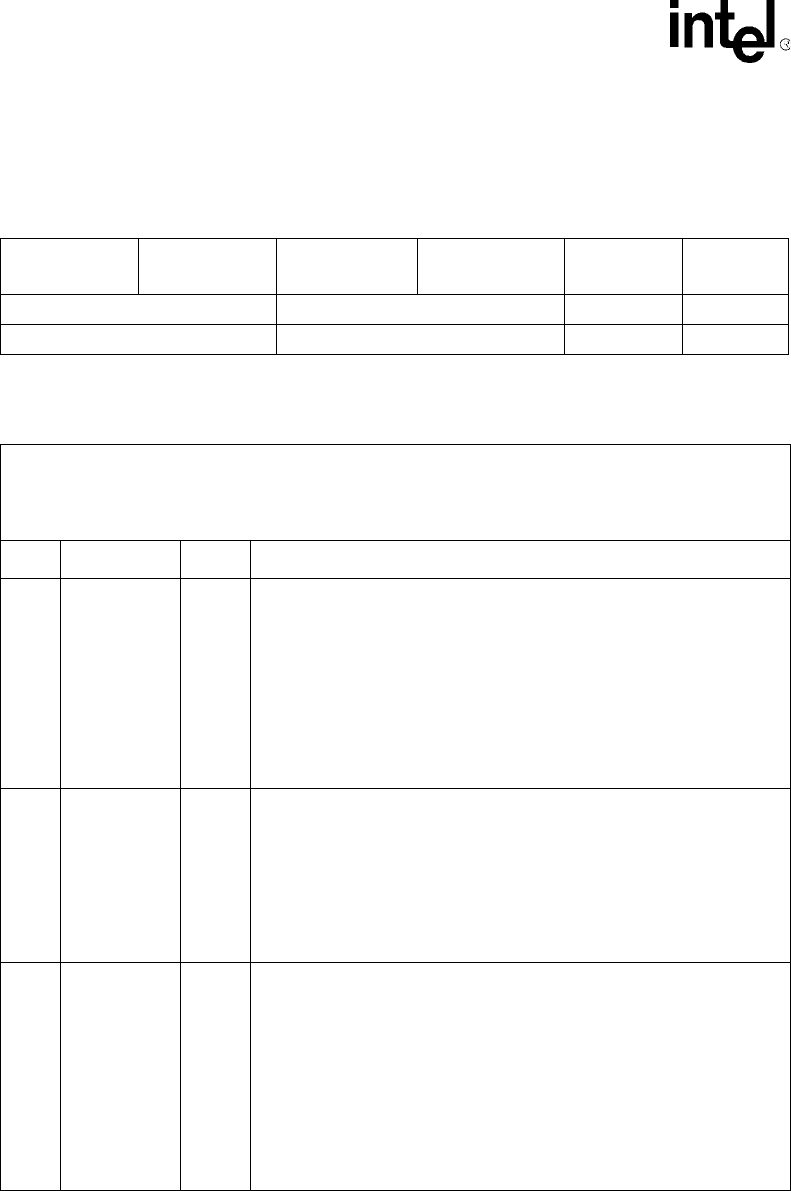

Table 76. Device-Specific Control and Status Address Map

Byte 3 Byte 2 Byte 1 Byte 0

Primary

Offset

Secondary

Offset

Chip Control 1 Chip Control 0 CCh CCh

Chip Status D0h D0h

Table 77. Chip Control 0 Register (Sheet 1 of 4)

This register may be preloaded by serial ROM or programmed by the local processor before host

configuration.

• Primary byte offset: CD:CCh

• Secondary byte offset: CD:CCh

Bit Name R/W Description

0

Master Abort

Mode

R/W

Controls the 21555’s behavior on the initiator bus when a master abort

termination occurs in response to a delayed transaction initiated by the

21555 on the target bus.

• When 0, the 21555 asserts TRDY# in response to a delayed

transaction, and returns FFFFFFFFh if a read. For posted writes,

SERR is not asserted on the initiator bus.

• When 1, the 21555 returns a target abort in response to a delayed

transaction. For posted writes, SERR will be asserted (if otherwise

enabled) on the initiator bus.

• Reset value is 0

1

Memory Write

Disconnect

Control

R/W

Controls the disconnect boundary for memory writes. This bit does not

apply to MWI commands.

• When 0, the 21555 disconnects memory writes either on an aligned 4

KB boundary, a page boundary less than 4 KB (Upstream Memory

Range 2 only) or when the posted write queue is full.

• When 1, the 21555 disconnects memory write on an aligned cache

line boundary, or when the posted write queue is full.

• Reset value is 0

2

Primary

Master

Timeout

R/W

Sets the maximum number of PCI clock cycles that the 21555 waits for an

initiator on the primary bus to repeat a delayed transaction request. The

counter starts when the delayed transaction completion is ready to be

returned to the initiator. When the initiator has not repeated the transaction

at least once before the counter expires, the 21555 discards the delayed

transaction from its queues.

• When 0, the primary master timeout counter is 2

15

PCI clock cycles, or

0.983 ms for a 33

-MHz bus.

• When 1, the value is 2

10

PCI clock cycles, or 30.7 µs for a 33-MHz

bus.

• Reset value is 0