88 21555 Non-Transparent PCI-to-PCI Bridge User Manual

Parallel ROM Interface

8.6 Access Time and Strobe Control

The 21555 controls both the access time and the read and write strobe timing through the ROM Setup CSR.

The access time is specified as a multiple of the p_clk signal and must be set to 8, 16, 64, or 256 times the length of

a p_clk cycle when p_clk is operating at 33 MHz or below, and 16, 32,128, or 512 times the length of a p_clk cycle

when p_clk is operating above 33 MHz. This specifies the number of p_clk cycles that the 21555 asserts pr_cs_l.

The reset value is 8 times the 33 MHz p_clk cycle time or 16 times the 66 MHz p_clk cycle time.

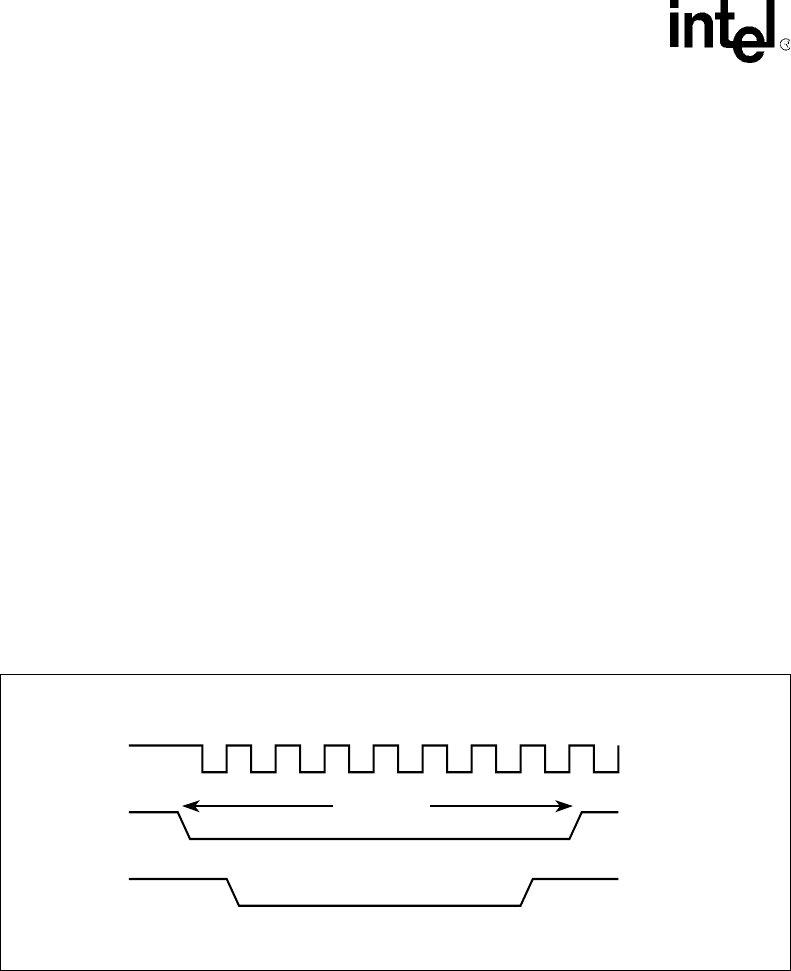

The read and write strobe timing of pr_rd_l and pr_wr_l is given as an 8-bit mask. Each bit corresponds to one

eighth of the access time, which can be 1, 2, 8, or 32 p_clk cycles when p_clk is operating at 33 MHz or below and

2, 4, 16, or 64 p_clk cycles when p_clk is operating above 33MHz. Bit 0 corresponds to the first cycle. When a bit

is a 0 (zero), the read or write strobe is deasserted. When the bit is a 1, the read or write strobe is asserted. Signal

pr_cs_l is asserted at the beginning of the first cycle and deasserted at the end of the last cycle. The reset value for

the strobe mask is 01111110b. Since the reset value of the access time is either 8 each 33 MHz p_clk cycles or 16

each 66 MHz p_clk cycles, this means a read or write access has the following timing (at

33 MHz), also shown in Figure 17:

• Cycle 1: assert pr_cs_l.

• Cycle 2 through 7: both pr_cs_l and pr_rd_l or pr_wr_l asserted.

• Cycle 8: deassert pr_rd_l or pr_wr_l.

• Cycle 9: deassert pr_cs_l.

Figure 17. Read and Write Strobe Timing

A7472-01

pr_wr_l

pr_rd_l

pr_cs_l

p_clk

1

2

34

5

67

89

Access Time