174 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.8 Scratchpad Registers

See Chapter 11 for theory of operation information.

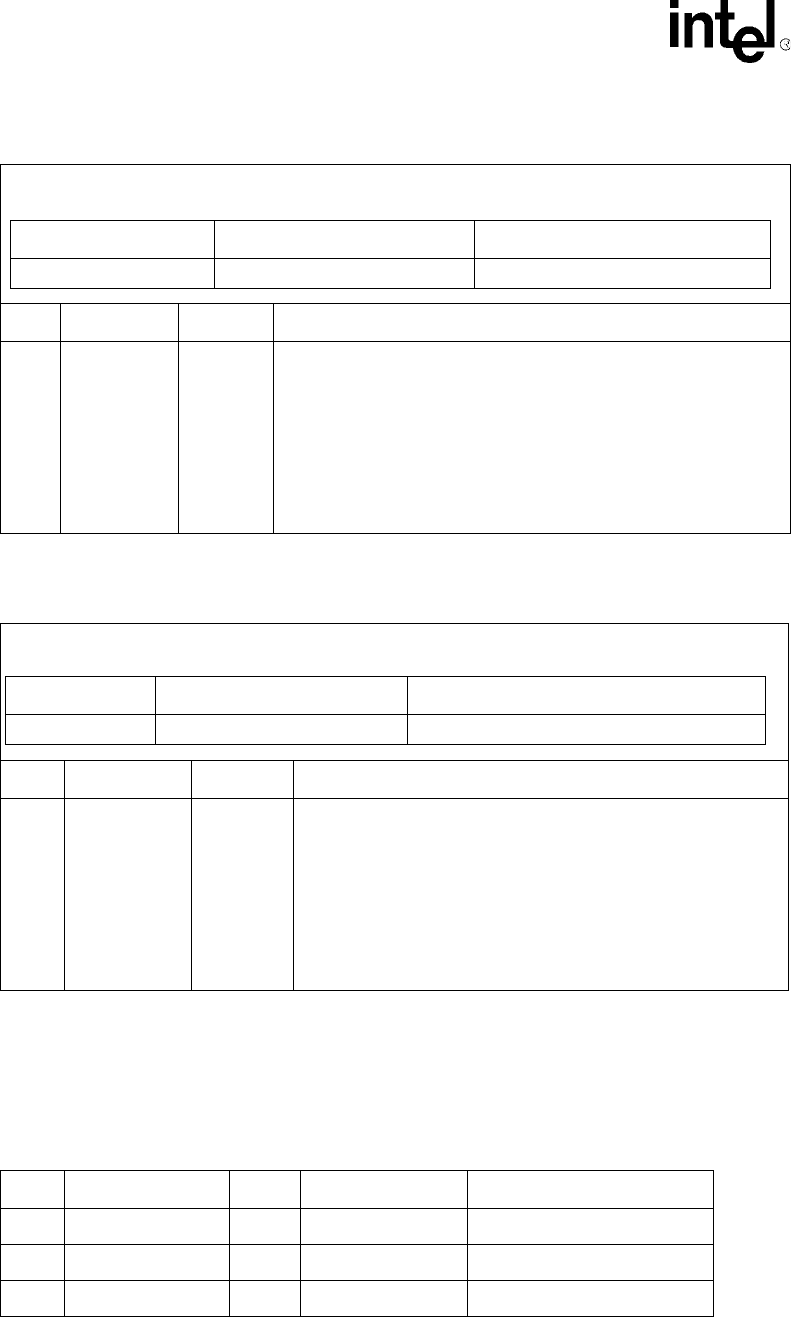

Table 104. Primary Clear IRQ Mask and Secondary Clear IRQ Mask Registers

Bit Name R/W Description

15:0 CLR_IRQM R/W1TC

• When 0, an interrupt is generated on the 21555’s primary or

secondary interface when the corresponding Primary or

Secondary Interrupt Request bit is a 1.

• When 1, the corresponding interrupt request bit cannot generate

an interrupt.

Writing a 1 to a bit in this register clears the IRQ Mask bit to 0.

Writing a 0 to any bit in this register has no effect. Reading this

register returns the current status of the IRQ Mask bits.

• Reset value is FFFFFFFFh

Table 105. Primary Set IRQ Mask and Secondary Set IRQ Mask Registers

Bit Name R/W Description

15:0 SET_IRQM R/W1TS

• When 0, an interrupt is generated on the 21555’s primary or

secondary interface when the corresponding Primary or

Secondary Interrupt Request bit is a 1.

• When 1, the corresponding interrupt request bit cannot

generate an interrupt.

Writing a 1 to a bit in this register sets the IRQ Mask bit to 1.

Writing a 0 to any bit in this register has no effect. Reading this

register returns the current status of the IRQ Mask bits.

• Reset value is FFFFFFFFh

Table 106. Scratchpad 0 Through Scratchpad 7 Registers (Sheet 1 of 2)

Bit Name R/W Byte Offset: Description

31:0 SCRATCH0 R/W 0AB:0A8h 32-bit scratchpad register 0.

31:0 SCRATCH1 R/W 0AF:0ACh 32-bit scratchpad register 1.

31:0 SCRATCH2 R/W 0B3:0B0h 32-bit scratchpad register 2.

These registers affect primary and secondary interrupts in the same way and are described

Primary Clear IRQ Mask Secondary Clear IRQ Mask

Byte Offset: 0A1:0A0h 0A3:0A2h

These registers affect primary and secondary interrupts in the same way and are described together.

Offsets Primary Set IRQ Mask Secondary Set IRQ Mask

Byte 0A5:0A4h 0A7:0A6h