21555 Non-Transparent PCI-to-PCI Bridge User Manual 71

Initialization Requirements

6.4.1 Transitions Between Power Management States

The 21555 is put into a different power state by writing the Power State bits in the Power Management Control and

Status configuration register. Table 19 shows the actions that the 21555 takes when transitioning between power

states. Although any transition to a lower power state is allowed, all transitions to a higher power state must go to

D0.

6.4.2 PME# Support

The 21555 provides optional PME# support. Since the 21555 provides the subsystem Power Management Interface

registers, the 21555 must also be the source of the PME# signal for the subsystem. The 21555 implements a

primary bus PME# output signal, p_pme_l, that is asserted when the subsystem wants to generate a power

management event. The 21555 implements a secondary bus power management input signal, s_pme_l, that the

subsystem asserts to notify the 21555 of this power management event.

The 21555 asserts p_pme_l when all of the following are true:

• The 21555 detects s_pme_l asserted low.

• PME# support for the current power state of the 21555 is enabled, as indicated in the Power Management

Capabilities register.

• The PME_En bit is set to a 1 in the Power Management Control and Status register.

When the first two conditions have both been met, the 21555 sets the PME Status bit in the Power Management

Control and Status register.

Once p_pme_l has been asserted, the 21555 deasserts the signal if either of the following conditions are true:

• The PME Status bit is cleared in the Power Management Control and Status register.

• The PME_En bit is cleared in the Power Management Control and Status register.

The 21555 assumes that s_pme_l is deasserted before the PME_Status bit is cleared in the Power Management

Control and Status register. Otherwise, multiple assertions of p_pme_l may occur. When PME# isolation circuitry

is required on the primary interface, it must be implemented externally.

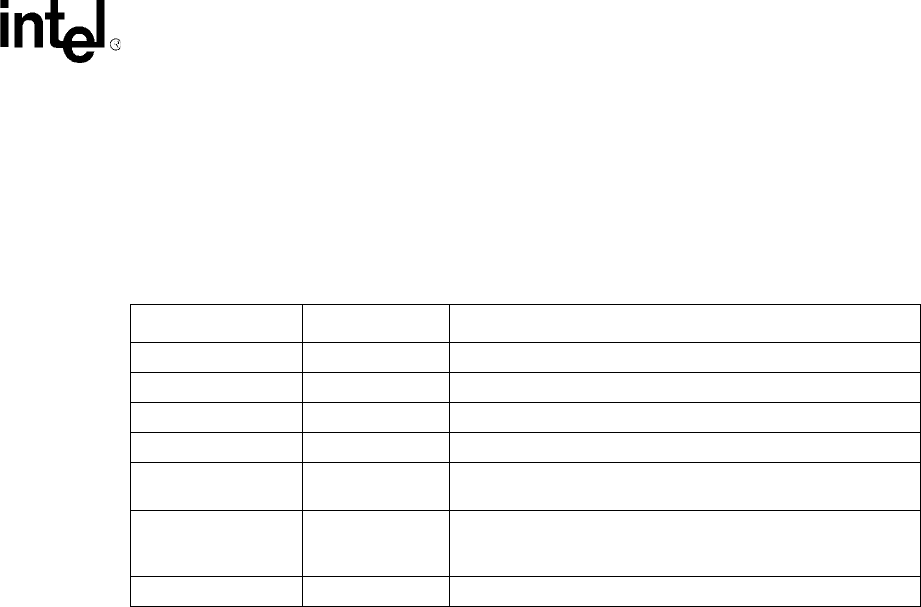

Table 19. Power Management Actions

Original Power State Next Power State Action

D0 D1 No action. Subsystem should have been notified by driver.

D0, D1 D2 No action. Subsystem should have been notified by driver.

D0, D1, D2 D3

hot

No action. Subsystem should have been notified by driver.

Any State D3

cold

No action. Powered off.

D1, D2 D0

Set “Transition to D0” status bit and assert s_inta_l when not

masked for that event.

D3

hot

D0

The 21555 performs a chip reset and asserts s_rst_l for 100 ms.

The 21555 performs a serial preload as soon as chip reset is

complete.

†

D3

cold

D0 Power on. Primary bus reset asserts. No special action needed.

† To adhere to the D3

hot

to D0 recovery time stated in the Power Management Specification, the local

processor may have to initialize the 21555 and clear the Primary Lockout Reset Value bit early in the

subsystem initialization process.