166 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

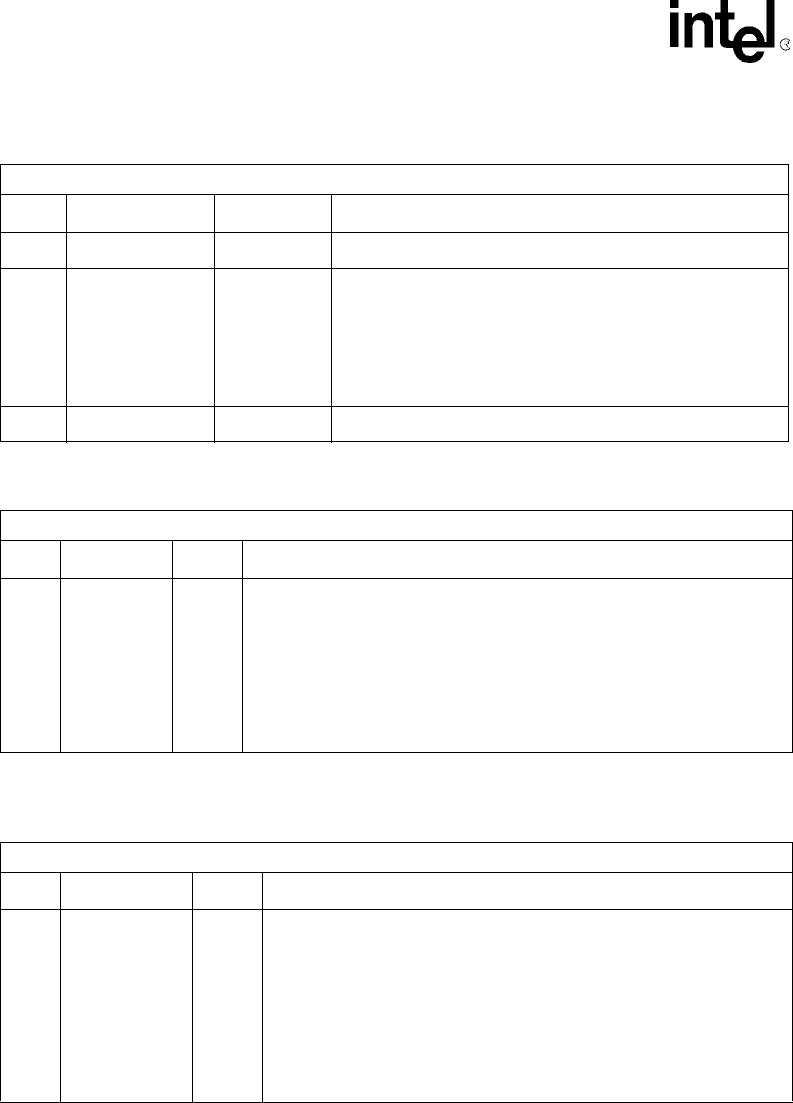

Table 84. I2O Inbound Post_List Interrupt Mask

Byte Offset: 3F:3Ch

Bit Name R/W Description

2:0 Reserved R Reserved. Read only as 0.

3

Inbound Post

Mask

R/W

Interrupt mask for Inbound Post_List Status.

• When 0, the 21555 asserts s_inta_l when the Inbound

Post_List Status bit is a 1.

• When 1, the 21555 does not assert s_inta_l when the

Inbound Post_List Status bit is a 1.

• Reset value is 1

31:4 Reserved R Reserved. Read only as 0.

Table 85. I2O Inbound Queue

Byte Offset: 43:40h

Bit Name R/W Description

31:0

I2O_IN (P)

Reserved (S)

R/(WP)

This register controls the host processor access to the I2O inbound queue.

When this register is read from the primary bus, the 21555 returns the value

from the head of the I2O inbound Free_List. When this register is written

from the primary bus, the 21555 writes the data to the tail of the inbound

Post_List. Accesses from the secondary bus are treated as reserved. The

actual location of the inbound queue lists are in local memory, and the initial

location of the Free_List head and Post_List tail pointers must be

programmed by the local processor in the I2O Inbound Free_List Head

Pointer and I2O Inbound Post_List Tail Pointer registers.

Table 86. I2O Outbound Queue

Byte offset: 47:44h

Bit Name R/W Description

31:0

I2O_OUT (P)

Reserved (S)

R/(WP)

This register controls the host processor access to the I2O outbound

queue. When this register is read from the primary bus, the 21555

returns the value from the head of the I2O outbound Post_List. When this

register is written from the primary bus, the 21555 writes the data to the

tail of the outbound Free_List. Accesses from the secondary bus are

treated as reserved. The actual location of the outbound queue lists are

in local memory, and the initial location of the Post_List head and

Free_List tail pointers must be programmed by the local processor in the

I2O Outbound Post_List Head Pointer and I2O Outbound Free_List Tail

Pointer registers.