21555 Non-Transparent PCI-to-PCI Bridge User Manual 97

Arbitration 10

This chapter describes the arbitration signals. It also describes how the 21555 implements primary and secondary

PCI bus arbitration. See Chapter 16 for specific information about the Arbiter registers.

10.1 Primary PCI Bus Arbitration Signals

Table 23 describes the primary PCI bus arbitration signals.

10.2 Secondary PCI Bus Arbitration Signals

Table 24 describes the secondary PCI bus arbitration signals.

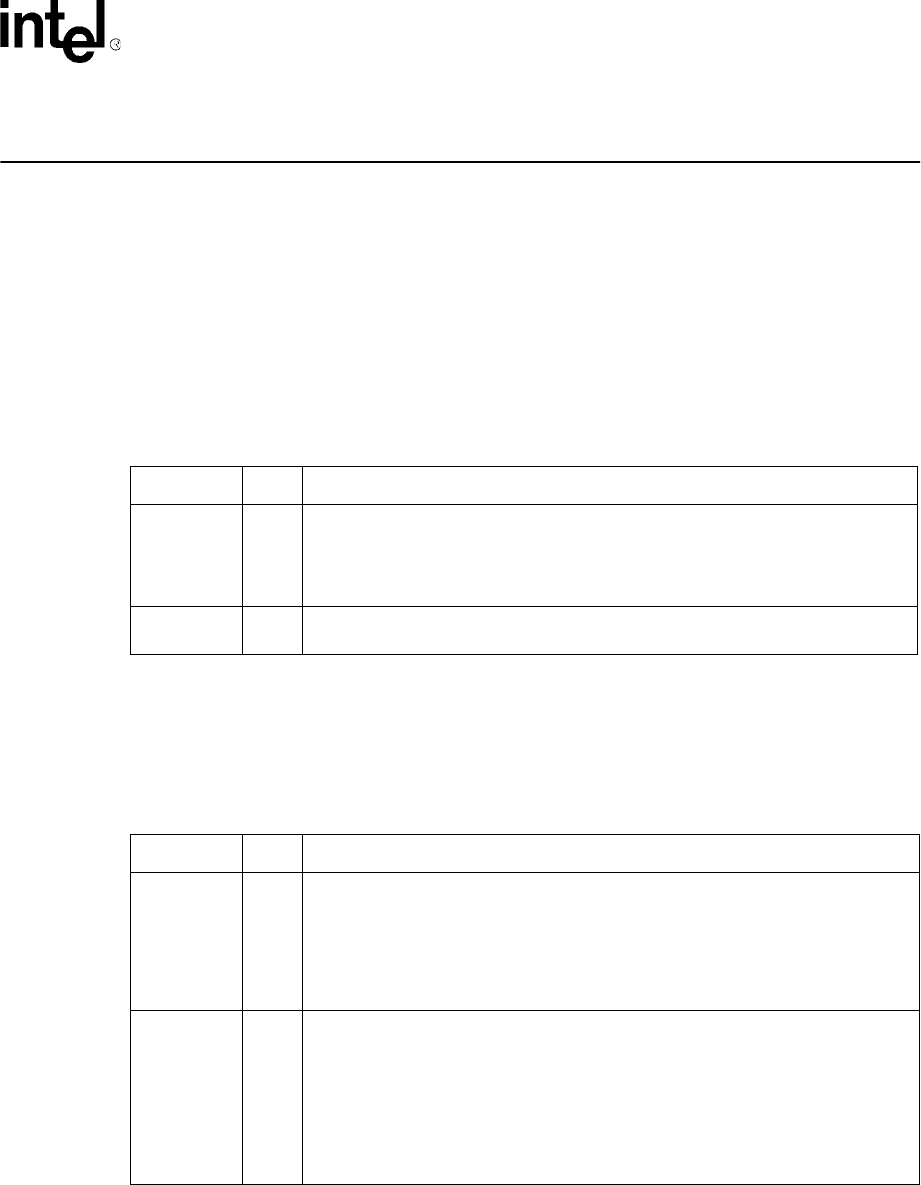

Table 23. Primary PCI Bus Arbitration Signals

Signal Name Type Description

p_gnt_l I

Primary PCI bus GNT#. When asserted, p_gnt_l indicates to the 21555 that access

to the primary bus is granted. The 21555 can start a transaction on the primary bus

when the bus is idle and p_gnt_l is asserted. When the 21555 has not requested use

of the bus and p_gnt_l is asserted, the 21555 drives p_ad, p_cbe_l, and p_par to

valid logic levels.

p_req_l TS

Primary PCI bus REQ#. Signal p_req_l is asserted by the 21555 to indicate to the

primary bus arbiter that it wants to start a transaction on the primary bus.

Table 24. Secondary PCI Bus Arbitration Signals

Signal Name Type Description

s_gnt_l[8:0] TS

Secondary PCI interface GNT#s. The 21555 secondary bus arbiter can assert one of

nine secondary bus grant outputs, s_gnt_l[8:0], to indicate that an initiator can start a

transaction on the secondary bus if the bus is idle. The 21555’s secondary bus grant

is an internal signal. A programmable two-level rotating priority algorithm is used.

When the internal arbiter is disabled, s_gnt_l[0] is reconfigured to be an external

secondary bus request output for the 21555. The 21555 asserts this signal whenever

it wants to start a transaction on the secondary bus.

s_req_l[8:0] I

Secondary PCI interface REQ#s. The 21555 accepts nine request inputs,

s_req_l[8:0], into its secondary bus arbiter. The 21555’s request input to the arbiter is

an internal signal. Each request input can be programmed to be in either a

high-priority rotating group or a low-priority rotating group. An asserted level on an

s_req_l pin indicates that the corresponding master wants to initiate a transaction on

the secondary PCI bus. When the internal arbiter is disabled, s_req_l[0] is

reconfigured to be an external secondary grant input for the 21555. In this case, an

asserted level on s_req_l[0] indicates that the 21555 can start a transaction on the

secondary PCI bus when the bus is idle.