21555 Non-Transparent PCI-to-PCI Bridge User Manual 173

List of Registers

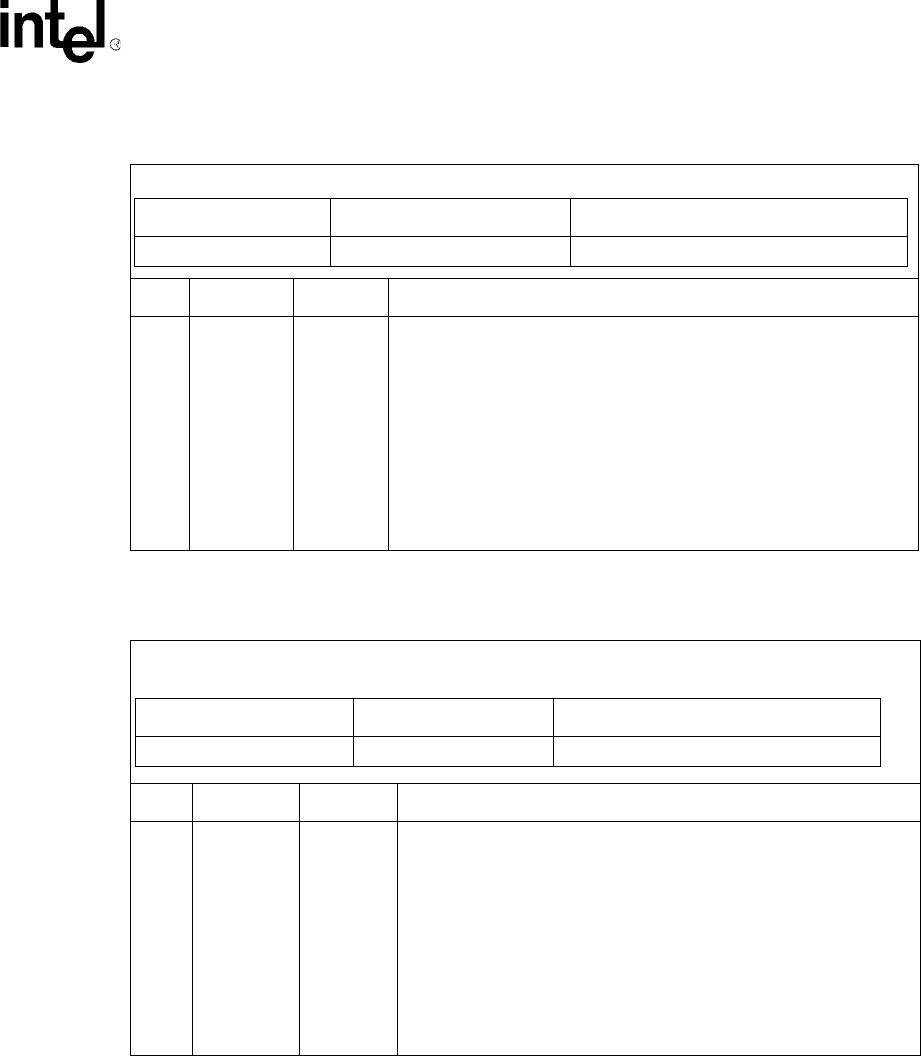

Table 102. Primary Clear IRQ and Secondary Clear IRQ Registers

These registers affect primary and secondary interrupts in the same way and are described together.

Bit Name R/W Description

15:0 CLR_IRQ R/W1TC

This register controls the state of the Primary or Secondary Interrupt

Request bits.

• When 0, Does not cause the corresponding primary or secondary

interrupt signal to be asserted.

• When 1, the primary or secondary interrupt signal is asserted when

the corresponding IRQ Mask bit is zero.

Writing a 1 to a bit in this register clears the corresponding interrupt

request bit to 0. Writing a 0 to any bit in this register has no effect.

Reading this register returns the current status of the interrupt

request bits.

• Reset value is 0

Table 103. Primary Set IRQ and Secondary Set IRQ Registers

Bit Name R/W Description

15:0 SET_IRQ R/W1TS

This register controls the state of the Primary or Secondary Interrupt

Request bits.

• When 0, Does not cause the corresponding primary or secondary

interrupt signal to be asserted.

• When 1, the primary or secondary interrupt signal is asserted if the

corresponding IRQ Mask bit is zero.

Writing a 1 to a bit in this register sets the corresponding interrupt

request bit to 1. Writing a 0 to any bit in this register has no effect.

Reading this register returns the current status of the interrupt

request bits.

• Reset value is 0

Primary Clear IRQ Secondary Clear IRQ

Byte Offset: 099:098h 09B:09Ah

These registers affect primary and secondary interrupts in the same way and are described together.

Offsets Primary Set IRQ Secondary Set IRQ

Byte 09D:09Ch 09F:09Eh