134 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

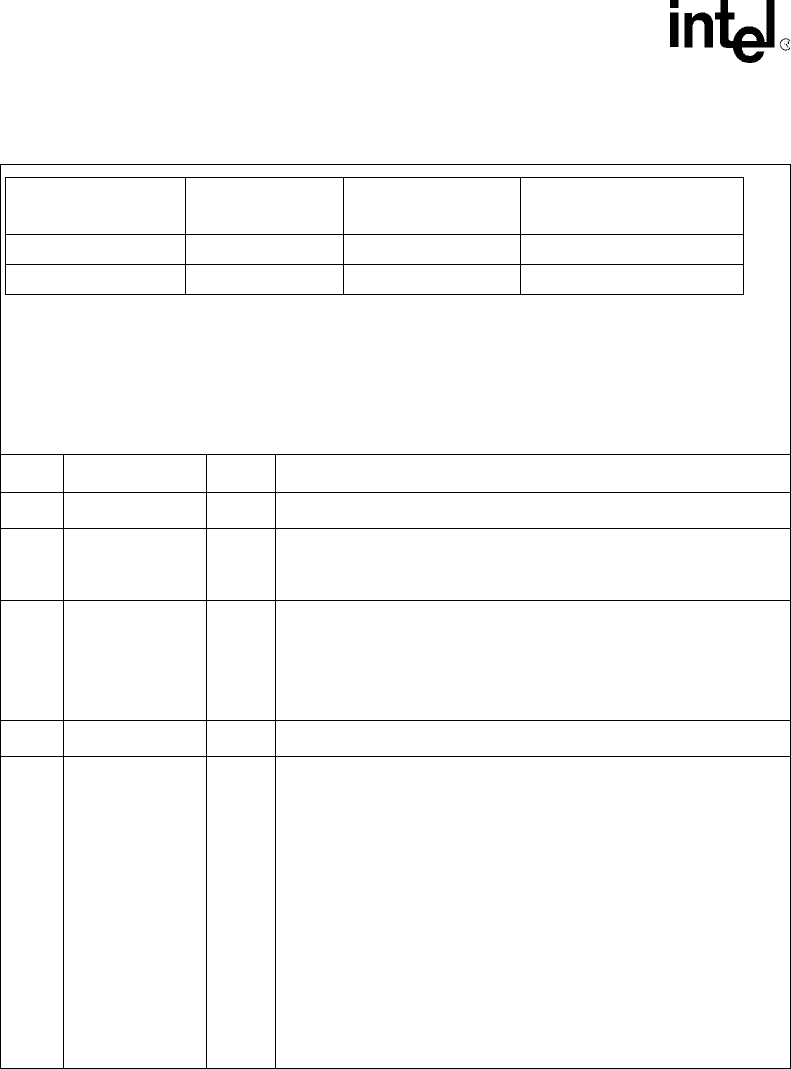

Table 38. Downstream Memory 2 and 3 BAR, and Upstream Memory 1 BAR

Bit Name R/W Description

0 Space Indicator R Reads only as 0 to indicate that memory space is requested.

2:1 Type R

Indicates size and location of this address space.

Reset value is 00 to indicate that this space can be mapped anywhere

in 32

-bit memory.

3 Prefetchable R

Indicates whether the region is prefetchable.

• When 0, nonprefetchable memory is requested (or the range is

disabled).

• When 1, prefetchable memory is requested.

• Reset value is 0

11:4 — R Returns 0.

31:12 Base Address R/W

These bits are used to indicate the size of the requested address range

and to set the base address of the range. Bits [31:12] of the

corresponding setup register determine the function of the

corresponding bit in this register.

• When a bit in the setup register is 0, the same bit in this register is

a read only bit and always returns 0 when read.

• When a bit in the setup register is one (1), the same bit in this

register is writable and returns the value last written when read.

This BAR is disabled by writing bit [31] of the setup register to zero.

For the Downstream Memory 3 BAR, bit [31] of the Upper 32 Bits setup

register must also be 0 to disable that range. The minimum size for this

address range is 4 K. The maximum size is 2GB, except for the

Downstream Memory 3 BAR which may use 64

-bit addressing and

have a maximum window size of 2

63

bytes.

• Reset value is Read only as 0 (range is disabled).

These registers are similar and are described together.

These registers define address ranges in which memory transactions on the primary interface of the 21555

are forwarded to the secondary interface for the downstream BARs, and in which memory transactions on

the secondary interface are forwarded to the primary interface for the upstream BAR.

The corresponding setup registers load from the SROM or the local processor before configuration

software running on the host processor can access these registers. Local processor access of the setup

registers is before the Primary Lockout Reset Value bit is clear.

Offsets

Downstream

Memory 2 BAR

Downstream

Memory 3 BAR

Upstream

Memory 1 BAR

Primary byte 1F:1Ch 23:20h 5F:5Ch

Secondary byte 5F:5Ch 63:60h 1F:1Ch