21555 Non-Transparent PCI-to-PCI Bridge User Manual 183

List of Registers

16.11 Arbiter Control

This chapter describes the arbitration control registers. See Chapter 10 for theory of operation information.

16.12 Error Registers

This section describes the primary and secondary SERR# disable registers. See Chapter 12 for theory of operation

information.

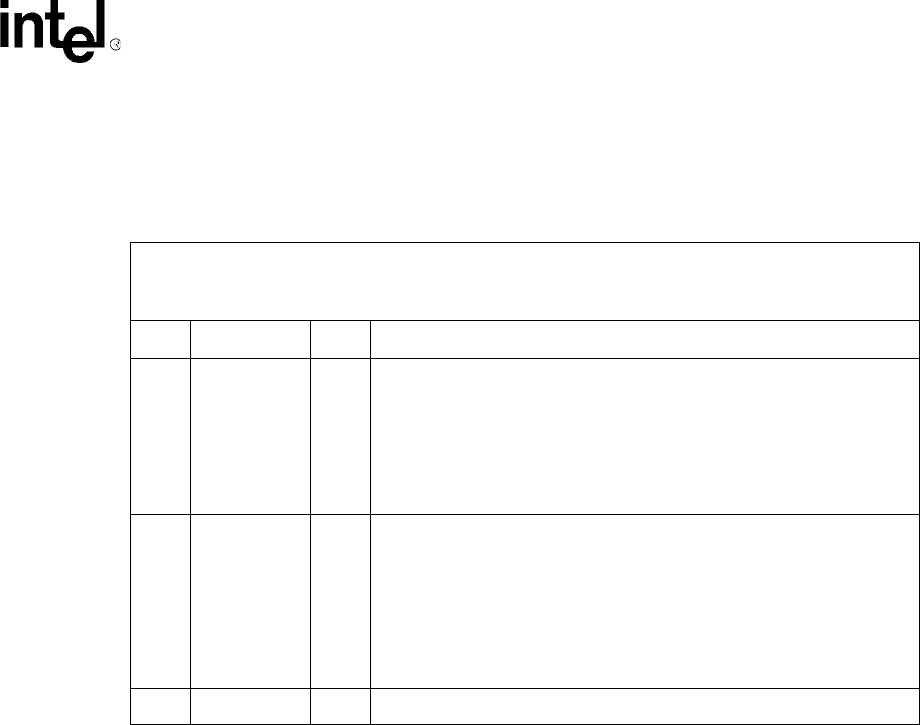

Table 115. Arbiter Control Register

This register may be preloaded by serial ROM or programmed by local processor before host configuration.

• Primary byte offset: D3:D2h

• Secondary byte offset: D3:D2h

Bit Name R/W Description

9:0 Arbiter Control R/W

Each bit controls whether a secondary bus master is assigned to the high

priority arbiter ring or the low priority arbiter ring. Bits [8:0] correspond to

request inputs s_req_l[8:0], respectively. Bit [9] corresponds to the internal

21555 secondary bus request.

• When 0, indicates that the master belongs to the low priority group.

• When 1, indicates that the master belongs to the high priority group.

• Reset value is 10 0000 0000b.

10

Bus Parking

Control

R/W

Controls whether the 21555 parks on itself or on the last master to use the

bus.

• When 0, during bus idle, the 21555 parks the bus on the last master to

use the bus.

• When 1, during bus idle, the 21555 parks the bus on itself. The bus

grant is removed from the last master and internally asserted to the

21555.

• Reset value is 0b.

15:11 Reserved R Reserved. Returns 0 when read.