Page 32 Epson Research and Development

Vancouver Design Center

S1D13705 Programming Notes and Examples

X27A-G-002-03 Issue Date: 02/01/22

5.3.1 Registers

Split screen operation is performed primarily by manipulating three register sets. Screen 1

Start Address and Screen 2 Start Address determine from where in display memory the first

and second images will be taken from. The Vertical Size registers determine how many

lines Screen 1 will use. The following is a description of the registers used to do split screen.

Screen 1 Vertical Size

These two registers form a ten bit value which determines the size of screen 1. When the

vertical size is equal to or greater than the physical number of lines being displayed there

is no visible effect on the display. When the vertical size value is less than the number of

physical display lines, operation is like this:

1. From the beginning of a frame to the number of lines indicated by vertical size the dis-

play data will come from the memory area pointed to by the Screen 1 Display Start

Address.

2. After vertical size lines have been displayed the system will begin displaying data

from the memory area pointed to by Screen 2 Display Start Address.

On thing that must be pointed out here is that Screen 1 memory is always displayed at the

top of the screen followed by screen 2 memory. This relationship holds true regardless of

where in display memory Screen 1 Start Address and Screen 2 Start Address are pointing.

For instance, Screen 2 Start Address may point to offset zero of display memory while

Screen 1 Start Address points to a location several thousand bytes higher. Screen 1 will still

be shown first on the display. While not particularly useful, it is even possible to set screen

1 and screen 2 to the same address.

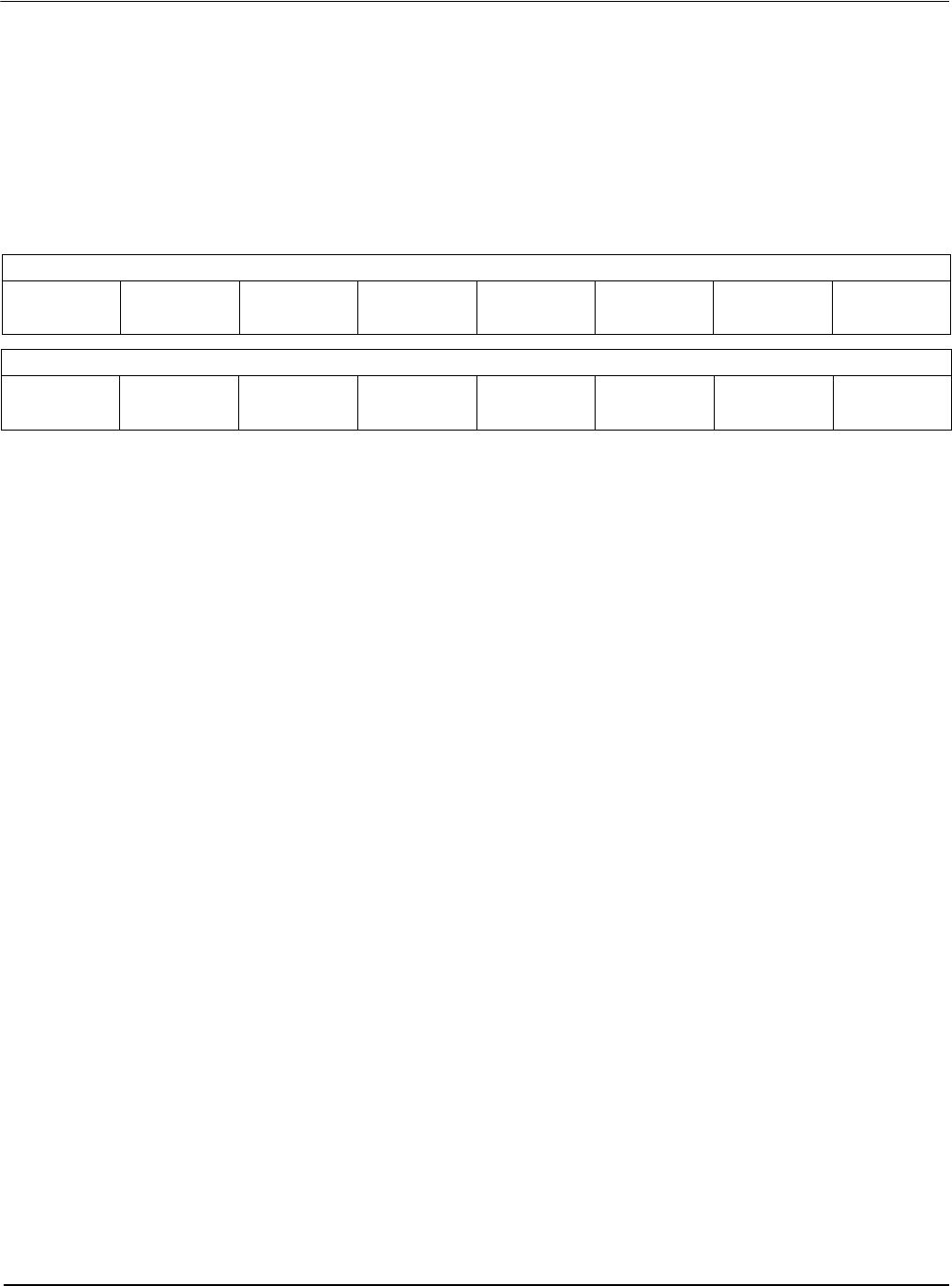

REG[12] Screen 1 Vertical Size (LSB)

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

REG[13] Screen 1 Vertical Size (MSB)

n/an/an/an/an/an/aBit 9Bit 8